|

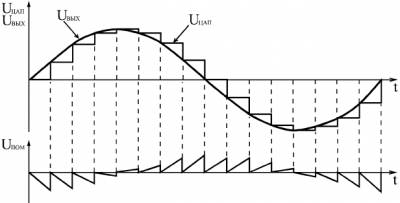

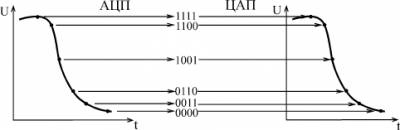

Цифровые генераторы (или, как их еще называют, синтезаторы) аналоговых сигналов произвольной формы часто используются при отладке различных аналоговых и аналого-цифровых устройств и систем. Они позволяют не только получить сигналы разных стандартных и нестандартных форм, но и обеспечить высокую точность задания амплитуды и частоты сигнала, не достижимые в случае обычных аналоговых генераторов. Цифровые генераторы работают обычно под управлением компьютеров или контроллеров, что обуславливает большие удобства пользователя и широкие возможности по заданию разнообразных форм сигналов и по их хранению. Мы будем разрабатывать довольно простой генератор, рассчитанный на звуковой диапазон частот выходного сигнала 20 Гц ... 20 кГц (период от 50 мкс до 50 мс). Генератор должен формировать сигналы произвольной формы с амплитудой, задаваемой управляющим кодом. Генератор должен работать в режиме автоматической (периодической) генерации, а также в режиме разовой генерации с остановкой генерации после окончания одного периода выходного сигнала. Управление работой генератора должно быть полностью цифровым. Отметим, что в реальности сигналы сложной формы, как правило, бывают низкочастотными. Они встречаются, например, при виброиспытаниях, в медицинской технике, в сейсмической технике и т.д. Высокочастотные сигналы обычно имеют довольно простую форму, например, синусоидальную. Поэтому наш простой генератор, рассчитанный на невысокие частоты, будет, тем не менее, удовлетворять требованиям довольно широкого спектра применений. Разработку генератора мы начнем "с конца", то есть с того выходного сигнала, который он должен формировать. Как уже отмечалось в лекции 13 , выходной сигнал ЦАП UЦАП представляет собой ступенчатую функцию, которую можно представить в виде суммы идеального ("гладкого") аналогового сигнала UВЫХ и пилообразного сигнала помехи UПОМ (рис. 15.9). Сигнал помехи UПОМ имеет основную частоту, равную частоте поступления входных кодов на ЦАП. Для сглаживания ступенек выходного сигнала ЦАП и приближения его к идеальному сигналу UВЫХ можно применить простой аналоговый фильтр низкой частоты (ФНЧ), который должен существенно ослаблять сигнал помехи, но не ослаблять полезный выходной сигнал генератора. В примере на рис. 15.9 частота полезного сигнала в 16 раз меньше частоты сигнала помехи, поэтому задача фильтрации не слишком сложна. Однако от генератора сигналов произвольной формы может понадобиться синтез выходных сигналов с крутыми фронтами (например, прямоугольных или пилообразных сигналов). В этом случае применение такого выходного фильтра низкой частоты может исказить выходные сигналы, затянув их фронты. Поэтому целесообразно предусмотреть два выхода генератора: один с низкочастотной фильтрацией, а другой без нее. Рис. 15.9. Цифровая генерация аналогового сигнала Помимо фильтра низкой частоты, выходной узел генератора сигналов должен содержать схему задания амплитуды выходного сигнала. В случае использования оперативной памяти для хранения кодов выборок выходного сигнала, схема задания амплитуды может и отсутствовать. При этом в память необходимо заносить коды выборок сигнала с нужной амплитудой. Однако такой подход не слишком удобен, так как он требует пересчета всех кодов выборок для каждой новой амплитуды сигнала выбранной формы. Гораздо удобнее сделать так, чтобы в памяти всегда хранились коды выборок сигнала с максимально возможной амплитудой, а выходной сигнал с ЦАП ослаблялся управляемым аттенюатором в нужное количество раз. В результате схема выходного узла генератора аналоговых сигналов будет включать в себя еще и управляемый аттенюатор, рассмотренный в разделе 7.1 (рис. 15.10). Рис. 15.10. Схема выходного узла генератора Аналоговый фильтр нижней частоты должен иметь коэффициент передачи в полосе пропускания, равный единице и частоту среза, обеспечивающую эффективное подавление сигнала помехи. Тип схемы фильтра и его порядок не слишком важны. Для удобства пользователя целесообразно сделать фильтр неинвертирующим, чтобы выходные сигналы на обоих выходах генератора ( UВЫХ1 и UВЫХ2 ) были одной полярности. Аттенюатор управляется 8-разрядным кодом амплитуды, что обеспечивает коэффициент деления сигнала

...

Читать дальше »

Категория:

15. Лекция: Разработка более сложных цифровых устройств

|

Просмотров:

2211

|

|

Дата:

12.03.2012

|

|

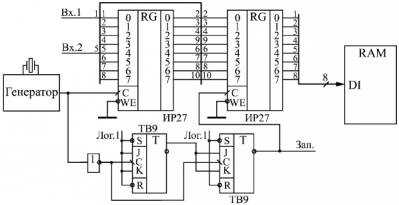

Разработка логического анализатора Логический анализатор — это контрольно-измерительный прибор, предназначенный для запоминания (фиксации) и последующего анализа (например, просмотра на экране) временных диаграмм большого количества цифровых сигналов. Логические анализаторы используются при динамической отладке различных цифровых устройств и систем, а также при контроле их работы. Совершенно незаменимы они при разработке и отладке различных микропроцессорных систем, контроллеров, компьютеров, где используется большое количество многоразрядных шин цифровых сигналов. Именно логические анализаторы позволяют разработчику увидеть те временные диаграммы, которые он рисует на бумаге при проектировании своего устройства, причем увидеть их в реальном масштабе времени, посмотреть, как работает устройство на своей нормальной рабочей скорости. Логический анализатор по своему назначению близок к осциллографу, так как он также позволяет наблюдать на экране временные диаграммы сигналов. Но существуют и существенные отличия логического анализатора от обычного (не цифрового) осциллографа: Логический анализатор работает только с цифровыми, то есть двухуровневыми (реже трехуровневыми) сигналами, а осциллограф — с аналоговыми сигналами, имеющими бесконечно большое число разрешенных уровней. Логический анализатор имеет большое количество входных линий (обычно от 16 до 64), то есть позволяет одновременно фиксировать множество входных сигналов, а осциллографы обычно позволяют одновременно увидеть не более четырех входных сигналов. Логический анализатор работает в режиме однократного запоминания временных диаграмм (как запоминающий осциллограф). То есть анализатор запоминает состояния входных сигналов в течение заданного времени (называемого окном регистрации), а затем дает возможность анализировать зафиксированные последовательности. Осциллограф же работает обычно в режиме непрерывной развертки, то есть он не запоминает формы входного сигнала и позволяет наблюдать только повторяющиеся, периодические сигналы. Логический анализатор предусматривает возможность так называемой предпусковой регистрации. Эта возможность предусматривается и в цифровых осциллографах, но ее нет в аналоговых осциллографах. Рассмотрим подробнее, что такое предпусковая регистрация. Процесс регистрации входных сигналов (или отображения их на экране в обычном осциллографе) всегда должен быть привязан к какому-то моменту времени, к какому-то внешнему событию, называемому запуском. Иначе разобраться в отображаемых сигналах будет совершенно невозможно. Например, в осциллографах моментом запуска обычно является момент превышения входным исследуемым сигналом установленного порога. Сигналом запуска может служить и специальный внешний синхронизирующий сигнал. В логических анализаторах в качестве запуска обычно используется момент появления на входах заданного уровня или заданной последовательности одного или нескольких входных сигналов. В обычных осциллографах отображение формы входного сигнала (или входных сигналов) начинается в момент запуска, то есть на экране видно только то, что происходило со входными сигналами после момента запуска. Такая регистрация может быть названа послепусковой. Можно также сказать, что точка запуска всегда находится в начале окна регистрации (рис. 15.1). Рис. 15.1. Послепусковая регистрация в аналоговых осциллографах В логических анализаторах (и в цифровых осциллографах) существует возможность увидеть и зафиксировать не только то, что было после запуска, но еще и то, что происходило в течение определенного времени до момента запуска. Именно эта регистрация до момента запуска и называется предпусковой регистрацией. В этом случае точка запуска может находиться и в начале, и в середине, и в конце окна регистрации (рис. 15.2). Понятно, что такая возможность очень удобна, так как, выбирая величину длительности предпусковой регистрации, можно увидеть те события, временная привязка к началу которых затруднена или попросту невозможна. Длительность (глубина) предпусковой регистрации может быть постоянной (например, равной половине длительности окна регистрации) или переменной (то есть задаваться пользователем в пределах от нуля до полной длительности окна регистрации). При переменной глубине предпусковой регистрации точка запуска может располагаться в любой точке окна регистрации — от его начала до конца. С точки зрения схемотехники, логический анализатор представляет собой быстродействующую буферную оперативную память, раб

...

Читать дальше »

Категория:

15. Лекция: Разработка более сложных цифровых устройств

|

Просмотров:

2647

|

|

Дата:

12.03.2012

|

|

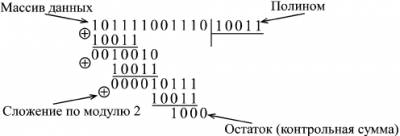

Разработка вычислителя контрольной суммы Различные контрольные суммы широко применяются в цифровых устройствах и системах для контроля правильности хранения или передачи массивов информации. Суть этого метода контроля проста: к хранимому или передаваемому информационному массиву присоединяется небольшой контрольный код (обычно от 1 разряда до 32 разрядов), в котором в свернутом виде содержится информация обо всем массиве. При чтении или получении этого массива еще раз вычисляется тот же самый контрольный код по тому же самому алгоритму. Если этот вновь вычисленный код равен тому коду, который был присоединен к массиву, то считается, что массив сохранен или передан без ошибок. Логика здесь следующая: контрольный код (он же контрольная сумма ) гораздо меньше контролируемого массива, поэтому вероятность искажения контрольной суммы гораздо меньше, чем вероятность искажения массива. Если же исказятся как массив, так и контрольная сумма, то вероятность того, что эти искажения не будут замечены при повторном подсчете контрольной суммы, крайне мала. Существует, правда, вероятность, что массив будет искажен в нескольких местах таким образом, что контрольная сумма от этих искажений никак не изменится, но такая вероятность также обычно мала. Контрольные суммы применяются при хранении данных в памяти (оперативной и постоянной), при хранении данных на магнитных носителях (дисках, лентах), в локальных и глобальных сетях передачи информации. В случае защиты контрольной суммой хранимой информации можно определить, что данный массив (файл, сектор на диске) испорчен и его нельзя использовать. В случае защиты контрольной суммой передаваемой по сети информации приемник может потребовать от передатчика повторной передачи искаженного массива. Существует множество способов вычисления контрольной суммы, различающихся степенью сложности вычисления и надежностью выявления ошибок. Но наибольшее распространение получил в настоящее время так называемый "циклический метод контроля по избыточности" или CRC (Cyclic Redundancy Check), при котором применяется циклическая контрольная сумма. Вычисляется циклическая контрольная сумма следующим образом. Весь массив информации рассматривается как одно N-разрядное двоичное число, где N — количество бит во всех байтах массива. Для вычисления контрольной суммы это N-разрядное число делится на некоторое постоянное число ( полином ), выбранное специальным образом (но делится не просто, а по модулю 2). Частное от этого деления отбрасывается, а остаток как раз и используется в качестве контрольной суммы. Мы не будем углубляться в математическое обоснование этого метода. Интересующиеся читатели могут обратиться к специальной литературе. Здесь же мы отметим только, что данный метод выявляет одиночные ошибки в массиве с вероятностью 100%, а любое другое количество ошибок с вероятностью, примерно равной 1–2-n, где n — количество разрядов контрольной суммы (это верно только при условии, что N гораздо больше n, что, впрочем, почти всегда выполняется). Например, при n = 8 данная вероятность составит 0,996, для n = 16 она будет равна 0,999985, а для n = 32 она будет 0,9999999997672. Иначе говоря, почти все ошибки будут выявляться. А теперь кратко поясним, что такое деление по модулю 2. Пусть массив (последовательность бит) имеет следующий вид: 101111001110 (для простоты берем небольшую разрядность). Число, на которое делим (называемое обычно образующим полиномом ) возьмем 10011. Как оно выбирается? Оно должно делиться по модулю 2 без остатка только на единицу и само на себя (то есть это должно быть простое число в смысле деления по модулю 2). Разрядность полинома берется на единицу большая, чем требуемая разрядность контрольной суммы (остатка от деления). Так, чтобы получить 8-разрядный остаток (8-разрядную контрольную сумму), надо брать 9-разрядный полином. В нашем случае полином 5-разрядный, следовательно, остаток будет 4-разрядный. Для получения 8-разрядного остатка можно использовать, например, полином 1 0001 1101 или 11D в 16-ричном коде. Деление по модулю 2 производится точно так же, как и привычное для нас деление "в столбик" (рис. 14.6), но вместо вычитания в данном случае используется поразрядное сложение по модулю 2, то есть каждый результирующий бит представляет собой функцию Исключающее ИЛИ от соответствующих битов слагаемых. Частное от деления нас не интересует, а остаток, равный в нашем примере 1000, и будет циклической контрольной суммой. Рис. 14.6. Вычисление циклической контрольной суммы К

...

Читать дальше »

Категория:

14. Лекция: Разработка простых цифровых устройств

|

Просмотров:

1342

|

|

Дата:

12.03.2012

|

|

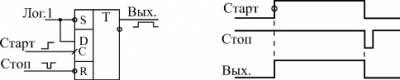

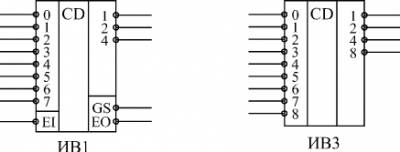

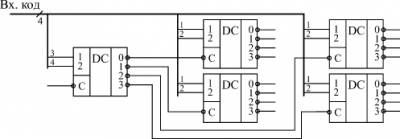

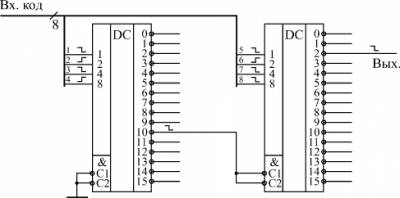

Разработка клавиатуры Различные клавиатуры с большим количеством клавиш (кнопок) широко используются в цифровых системах: в компьютерах, контроллерах, измерительных приборах, в бытовой технике. Основная задача любой клавиатуры довольно проста: она должна при любом нажатии на клавишу выдавать код номера этой клавиши и сигнал флага нажатия клавиши (строб этого кода). Получив этот сигнал флага, внешнее устройство читает код нажатой клавиши и предпринимает требуемые действия. Главная задача при проектировании клавиатуры состоит в минимизации аппаратных затрат и в обеспечении надежного срабатывания в любой ситуации. Существует масса схемотехнических решений этой задачи — от примитивных до сложнейших. Клавиатуры могут быть механическими, квазисенсорными или сенсорными, клавиатуры могут иметь жесткую логику работы или быть интеллектуальными, даже допускать перепрограммирование. Мы будем в качестве примера рассматривать самую простую механическую клавиатуру с жесткой логикой работы. Количество клавиш полноразмерной клавиатуры компьютера превышает сотню, поэтому мы будем проектировать клавиатуру на максимальное количество клавиш, равное 128. Естественно, клавиатура должна иметь защиту от дребезга механических контактов и должна корректно обрабатывать ситуацию одновременного нажатия нескольких клавиш. Примем, например, что при одновременном нажатии нескольких клавиш клавиатура должна выдавать код только одной из них. Примем также, что максимально возможный темп нажатия клавиш на клавиатуре не должен превышать 20 нажатий в секунду (это довольно много). Таким образом, основные требования к проектируемому устройству сформулированы. Начнем разработку. Очень часто удобным и эффективным приемом является начало разработки устройства "с конца". То есть проектирование начинается исходя из требуемого результата, из тех сигналов, которые устройство должно выдавать вовне и принимать извне. И только в конце проектирования разрабатывается та часть устройства, которая выполняет требуемую функцию. Такой подход гарантирует, что разработанное устройство не будет чрезмерно избыточным, не будет делать ничего лишнего, а также то, что оно корректно будет взаимодействовать с другими устройствами и системами. Этот принцип проектирования не универсален, порой выдержать его в течение всего процесса разработки трудно, но попробовать его применить к любому устройству никогда не помешает. В нашем случае необходимо сначала определиться, что должна выдавать вовне клавиатура. Обычно это задается техническим заданием, но мы примем, что наша клавиатура должна выдавать 7-разрядный двоичный номер нажатой клавиши (так как 27 = 128) и сопровождать его положительным сигналом флага нажатия. Сигнал флага и код клавиши должны сохраняться до тех пор, пока нажата клавиша. За это время (несколько миллисекунд) внешнее устройство должно успеть проанализировать сигнал флага и прочитать выходной код клавиатуры. Обычно данное требование не слишком жесткое. Альтернативное решение — сохранение кода нажатой клавиши и сигнала флага до момента чтения выходного кода внешним устройством — конечно же, снижает требование к быстродействию читающего внешнего устройства, однако оно может привести к тому, что некоторые нажатия клавиш останутся без реакции, не будут обработаны. Также необходимо определиться, как клавиатура будет вести себя при одновременном нажатии нескольких клавиш. Наиболее сложные, интеллектуальные клавиатуры выдают последовательно коды всех нажатых клавиш, запоминая их в буферной памяти. Но мы примем, что клавиатура должна выдавать только код одной из одновременно нажатых клавиш (первой по установленному порядку). Нажатия всех остальных клавиш одновременно с данной просто игнорируются. При проектировании механической клавиатуры важно решить, как будет обрабатываться неизбежно присутствующий дребезг механических контактов клавиш. Его можно обрабатывать как внутри клавиатуры, так и вне ее (то есть перенести эту функцию на внешнее устройство). Оба эти подхода имеют свои преимущества. Но наша клавиатура будет обрабатывать дребезг контактов самостоятельно. Принцип обработки выбираем очень простой: первое зафиксированное замыкание контактов клавиши считается началом нажатия, а конец нажатия определяется тогда, когда контакты будут разомкнуты в течение заданного интервала времени. В результате временная диаграмма работы разрабатываемой клавиатуры может быть упрощенно представлена в виде рис. 14.1. Здесь сигнал флага начинается при фиксации единичного сигнала с клавиши (это может быть как во время дребезга, так и после его окончания). После выставления флага фиксируется выходной код клавиши. После отпускания клавиши (нулевой сигнал), через время задержки tзад снимается сигнал флага. Время задержки должно быть заведомо больше времени дребезга

...

Читать дальше »

Категория:

14. Лекция: Разработка простых цифровых устройств

|

Просмотров:

1566

|

|

Дата:

12.03.2012

|

|

В лекции подробно рассматриваются примеры разработки простых цифровых устройств — клавиатуры и вычислителя контрольной суммы, начиная от анализа функций устройств и выделения основных узлов до проектирования принципиальных схем узлов и устройства в целом. Содержание Разработка клавиатуры Разработка вычислителя контрольной суммы В предыдущих лекциях были рассмотрены базовые элементы цифровой схемотехники и простейшие приемы проектирования узлов на их основе. Но для разработки сложных устройств и систем всех этих знаний порой оказывается недостаточно. Чтобы создать сложное устройство, необходимо еще владеть приемами системотехники, то есть уметь на основании анализа функций, которые должно выполнять устройство в целом, спроектировать его структуру, сформулировать принципы взаимодействия узлов, четко определить все задачи, которые должен решать каждый из узлов, выработать требования к отдельным узлам. Возможно, в результате всех этих шагов будет изменена сама первоначальная задача, будут переформулированы требования к создаваемому устройству, к его месту в системе, к принципам его взаимодействия с другими устройствами. И только потом, после всей этой предварительной работы уже можно переходить к разработке узлов, собственно к схемотехнике. Приемы системотехники сформулировать, формализовать, описать, даже перечислить гораздо сложнее, чем приемы схемотехники. Да и пользы от такой формализации зачастую немного. Проектирование сложного, надежно работающего цифрового устройства с минимальными аппаратными затратами сродни искусству и требует от разработчика определенных способностей, даже таланта. Научить этому практически невозможно. Более того, попытка научить системотехнике может даже принести вред, так как ограничит творческие способности разработчика несколькими жесткими стандартными алгоритмами. Однако можно показать несколько простейших примеров разработки, продемонстрировать последовательность шагов, которые необходимы при проектировании, которые могут встретиться в процессе создания устройств некоторых распространенных типов. Исходя из этих примеров, разработчик может в дальнейшем попробовать по аналогии создать что-то свое, более или менее совершенное, но обязательно работоспособное. Поэтому в данной лекции как раз и будут подробно рассмотрены несколько простых примеров проектирования сравнительно сложных устройств на всех этапах: от анализа решаемой задачи до создания полной принципиальной схемы. Примеры эти, конечно, не отражают и малой доли всех реально встречающихся задач, но относятся к различным классам цифровых устройств.

|

|

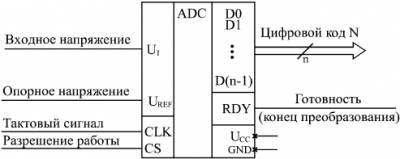

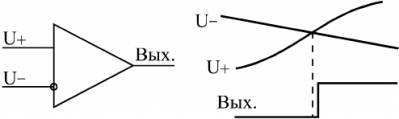

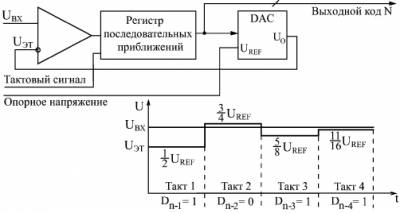

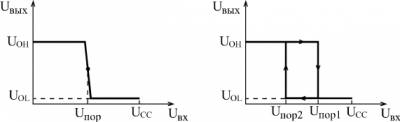

Применение АЦП Микросхемы АЦП выполняют функцию, прямо противоположную функции ЦАП, — преобразуют входной аналоговый сигнал в последовательность цифровых кодов. В общем случае микросхему АЦП можно представить в виде блока, имеющего один аналоговый вход, один или два входа для подачи опорного (образцового) напряжения, а также цифровые выходы для выдачи кода, соответствующего текущему значению аналогового сигнала (рис. 13.13). Часто микросхема АЦП имеет также вход для подачи тактового сигнала CLK, сигнал разрешения работы CS и сигнал, говорящий о готовности выходного цифрового кода RDY. На микросхему подается одно или два питающих напряжения и общий провод. В целом микросхемы АЦП сложнее, чем микросхемы ЦАП, их разнообразие заметно больше, и поэтому сформулировать для них общие принципы применения сложнее. Рис. 13.13. Микросхема АЦП Опорное напряжение АЦП задает диапазон входного напряжения, в котором производится преобразование. Оно может быть постоянным или же допускать изменение в некоторых пределах. Иногда предусматривается подача на АЦП двух опорных напряжений с разными знаками, тогда АЦП способен работать как с положительными, так и с отрицательными входными напряжениями. Выходной цифровой код N (n-разрядный) однозначно соответствует уровню входного напряжения. Код может принимать 2n значений, то есть АЦП может различать 2n уровней входного напряжения. Количество разрядов выходного кода n представляет собой важнейшую характеристику АЦП. В момент готовности выходного кода выдается сигнал окончания преобразования RDY, по которому внешнее устройство может читать код N. Управляется работа АЦП тактовым сигналом CLK, который задает частоту преобразования, то есть частоту выдачи выходных кодов. Предельная тактовая частота — второй важнейший параметр АЦП. В некоторых микросхемах имеется встроенный генератор тактовых сигналов, поэтому к их выводам подключается кварцевый генератор или конденсатор, задающий частоту преобразования. Сигнал CS разрешает работу микросхемы. Выпускается множество самых разнообразных микросхем АЦП, различающихся скоростью работы (частота преобразования от сотен килогерц до сотен мегагерц), разрядностью (от 6 до 24), допустимыми диапазонами входного сигнала, величинами погрешностей, уровнями питающих напряжений, методами выдачи выходного кода (параллельный или последовательный), другими параметрами. Обычно микросхемы с большим количеством разрядов имеют невысокое быстродействие, а наиболее быстродействующие микросхемы имеют небольшое число разрядов. Область применения любой микросхемы АЦП во многом определяется использованным в ней принципом преобразования, поэтому необходимо знать особенности этих принципов. Для выбора и использования АЦП необходимо пользоваться подробными справочными данными от фирмы-производителя. Рис. 13.14. Компаратор напряжения В качестве базового элемента любого АЦП используется компаратор напряжения (рис. 13.14), который сравнивает два входных аналоговых напряжения и, в зависимости от результата сравнения, выдает выходной цифровой сигнал — нуль или единицу. Компаратор работает с большим диапазоном входных напряжений и имеет высокое быстродействие (задержка порядка единиц наносекунд). Рис. 13.15. АЦП последовательного типа Существует два основных принципа построения АЦП: последовательный и параллельный. В последовательном АЦП входное напряжение последовательно сравнивается одним единственным компаратором с несколькими эталонными уровнями напряжения, и в зависимости от результатов этого сравнения формируется выходной код. Наибольшее распространение получили АЦП на основе так называемого регистра последовательных приближений (рис. 13.15). Входное напряжение подается на вход компаратора, на другой вход которого подается эталонное напряжение, ступенчато изменяющееся во времени. Выходной сигнал компаратора пода

...

Читать дальше »

|

|

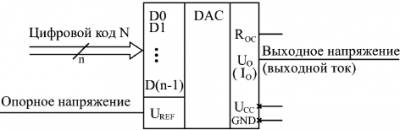

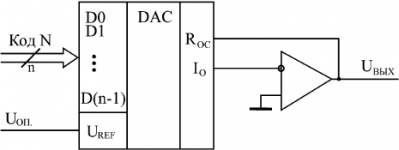

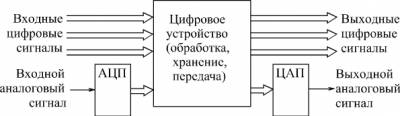

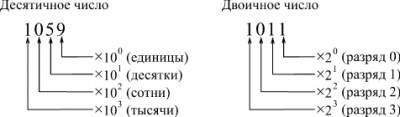

Как уже отмечалось во второй лекции, цифро-аналоговые преобразователи ( ЦАП, DAC — "Digital-to-Analog Converter") и аналого-цифровые преобразователи ( АЦП, ADC — "Analog-to-Digital Converter") главным образом применяются для сопряжения цифровых устройств и систем с внешними аналоговыми сигналами, с реальным миром. При этом АЦП преобразует аналоговые сигналы во входные цифровые сигналы, поступающие на цифровые устройства для дальнейшей обработки или хранения, а ЦАП преобразует выходные цифровые сигналы цифровых устройств в аналоговые сигналы (см.рис. 2.12). ЦАП и АЦП применяются в измерительной технике (цифровые осциллографы, вольтметры, генераторы сигналов и т.д.), в бытовой аппаратуре (телевизоры, музыкальные центры, автомобильная электроника и т.д.), в компьютерной технике (ввод и вывод звука в компьютерах, видеомониторы, принтеры и т.д.), в медицинской технике, в радиолокационных устройствах, в телефонии и во многих других областях. Применение ЦАП и АЦП постоянно расширяется по мере перехода от аналоговых к цифровым устройствам. В качестве ЦАП и АЦП обычно применяются специализированные микросхемы, выпускаемые многими отечественными и зарубежными фирмами. Сразу же надо отметить, что для грамотного и профессионального использования микросхем ЦАП и АЦП совершенно не достаточно знания цифровой схемотехники. Эти микросхемы относятся к аналого-цифровым, поэтому они требуют также знания аналоговой схемотехники, существенно отличающейся от цифровой. Практическое применение ЦАП и АЦП требует расчета аналоговых цепей, учета многочисленных погрешностей преобразования (как статических, так и динамических), знания характеристик и особенностей аналоговых микросхем (в первую очередь, операционных усилителей) и многого другого, что далеко выходит за рамки этой книги. Существует обширная литература, специально посвященная именно вопросам применения ЦАП и АЦП. Поэтому в данной лекции мы не будем говорить о специфике выбора и принципах включения конкретных микросхем ЦАП и АЦП мы будем рассматривать только основные особенности методов соединения ЦАП и АЦП с цифровыми узлами. Нас будет в первую очередь интересовать организация цифровых узлов, предназначенных для соединения с ЦАП и АЦП. Применение ЦАП В общем случае микросхему ЦАП можно представить в виде блока (рис. 13.1), имеющего несколько цифровых входов и один аналоговый вход, а также аналоговый выход. Рис. 13.1. Микросхема ЦАП На цифровые входы ЦАП подается n-разрядный код N, на аналоговый вход — опорное напряжение Uоп (другое распространенное обозначение — UREF ). Выходным сигналом является напряжение Uвых (другое обозначение — UO ) или ток Iвых (другое обозначение — IO ). При этом выходной ток или выходное напряжение пропорциональны входному коду и опорному напряжению. Для некоторых микросхем опорное напряжение должно иметь строго заданный уровень, для других допускается менять его значение в широких пределах, в том числе и изменять его полярность (положительную на отрицательную и наоборот). ЦАП с большим диапазоном изменения опорного напряжения называется умножающим ЦАП, так как его можно легко использовать для умножения входного кода на любое опорное напряжение. Кроме информационных сигналов, микросхемы ЦАП требуют также подключения одного или двух источников питания и общего провода. Обычно цифровые входы ЦАП обеспечивают совместимость со стандартными выходами микросхем ТТЛ. Чаще всего в случае, если ЦАП имеет токовый выход, его выходной ток преобразуется в выходное напряжение с помощью внешнего операционного усилителя и встроенного в ЦАП резистора RОС, один из выводов которого выведен на внешний вывод микросхемы (рис. 13.2). Поэтому, если не оговорено иное, мы будем в дальнейшем считать, что выходной сигнал ЦАП — напряжение UO. Рис. 13.2. Преобразование выходного тока ЦАП в выходное напряжение Суть преобразования входного цифрового кода в выходной аналоговый сигнал довольно проста. Она состоит в суммировании нескольких токов (по числу разрядов входного кода), каждый последующий из которых вдвое больше предыдущего. Для получения этих токов используются или транзисторные источники тока, или резистивные матрицы, коммутируемые транзист

...

Читать дальше »

|

|

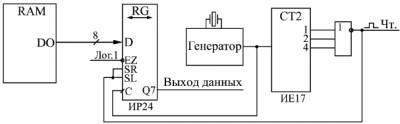

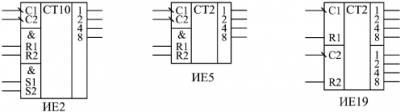

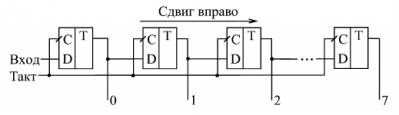

Улучшение параметров ОЗУ При применении оперативной памяти часто встает задача улучшить ее характеристики. О совместном включении нескольких микросхем с целью увеличения разрядности шины адреса и шины данных уже говорилось. Здесь же мы остановимся на задаче повышения быстродействия памяти, то есть увеличения предельной тактовой частоты, с которой можно записывать информацию в память и читать информацию из памяти. Наверное, самое распространенное и самое простое решение, позволяющее повысить быстродействие памяти, состоит в применении сдвиговых регистров. Сдвиговые регистры всегда имеют существенно большее быстродействие, чем память, так как они имеют гораздо более простую структуру. Частота следования тактовых импульсов этих регистров может достигать десятков и сотен мегагерц, тогда как память с такими параметрами найти трудно. Увеличение быстродействия памяти достигается с помощью сдвиговых регистров очень просто: уменьшение в несколько раз разрядности шины данных памяти позволяет во столько же раз увеличить частоту записи информации в память или чтения информации из памяти. Например, если необходимо в 8 раз увеличить частоту чтения информации из памяти, то надо соединить нужное количество микросхем памяти для увеличения разрядности шины данных в 8 раз, а затем применить на выходах данных схему (рис. 12.16) на основе 8-разрядного регистра сдвига. 8-разрядный код, читаемый из памяти, записывается в сдвиговый регистр, а затем сдвигается семь раз с частотой, в 8 раз большей, чем частота опроса памяти. И запись, и сдвиг производятся одним тактовым сигналом с генератора. Восемь тактовых импульсов отсчитываются синхронным счетчиком. Для управления работой регистра сдвига применен элемент 3ИЛИ-НЕ, выдающий положительный импульс в течение первой 1/8 периода опроса памяти. Этот же сигнал используется как строб чтения из памяти (своим задним фронтом он переключает адреса памяти). Рис. 12.16. Увеличение частоты чтения информации В случае необходимости увеличения частоты записи в память одного сдвигового регистра недостаточно. Дело в том, что информация в память записывается не по фронту сигнала, а по уровню, то есть записываемая информация должна сохраняться на входе памяти определенное время. Поэтому код с выхода сдвигового регистра необходимо перед записью в память переписать в параллельный регистр, где он будет затем храниться в течение всего периода записи в память. Схема, показанная на рис. 12.17, ускоряет частоту записи в память в 4 раза. Рис. 12.17. Увеличение частоты записи информации В данном случае в качестве регистра сдвига удобно использовать обычный параллельный регистр, срабатывающий по фронту, у которого выходы трех разрядов соединены со входами следующих разрядов. При этом из одного 8-разрядного регистра мы получаем два 4-разрядных регистра сдвига. 2-разрядная входная информация записывается в эти два 4-разрядных регистра сдвига, затем переписывается в параллельный регистр и только потом записывается в память. Для отсчета четырех импульсов тактового генератора применен 2-разрядный счетчик на двух JK-триггерах, включенных в счетном режиме, что позволяет несколько повысить быстродействие по сравнению со стандартными микросхемами счетчиков. Сигнал с выхода второго триггера записывает информацию в параллельный регистр, а также используется в качестве строба записи в память "Зап.". Большой недостаток оперативной памяти состоит в том, что информация, записанная в нее, исчезает при выключении источника питания. Поэтому часто используется дополнительный источник питания (гальваническая батарея или аккумулятор), который питает при выключении источника питания только микросхемы памяти. В данном случае очень удобны микросхемы ОЗУ, выполненные по КМОП технологии, ток потребления которых в статическом режиме (при неизменных входных и выходных сигналах) очень мал (порядка единиц микроампер). В результате получается так называемая энергонезависимая оперативная память, содержимое которой может легко перезаписываться, но не пропадает при выключении питания, как в ПЗУ. Схема энергонезависимой памяти (рис. 12.18) довольно проста, хотя и имеет ряд неочевидных особенностей.

|

|

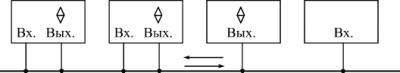

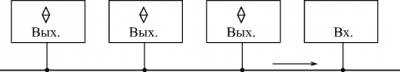

ОЗУ как информационный буфер Второе важнейшее применение микросхем оперативной памяти состоит в организации разнообразных информационных буферов, то есть буферной памяти для промежуточного хранения данных, передаваемых между двумя устройствами или системами. Суть информационного буфера состоит в следующем: передающее устройство записывает передаваемые данные в буфер, а принимающее устройство читает принимаемые данные из буфера (рис. 12.10). Рис. 12.10. Включение буферной памяти Такое промежуточное хранение позволяет лучше скоординировать работу устройств, участвующих в обмене данными, повысить их независимость друг от друга, согласовать скорости передачи и приема данных. Пусть, например, в качестве первого устройства выступает компьютер, а в качестве второго - кабель локальной сети. Компьютеру значительно удобнее выдавать данные со скоростью, определяемой его собственным быстродействием, но в локальную сеть надо передавать данные со строго определенной скоростью, задаваемой стандартом на сеть (например, 100 Мбит/с). Кроме того, компьютер, по возможности, не должен отвлекаться на контроль за текущим состоянием сети, за ее занятостью и освобождением. Поэтому буферная память в данном случае необходима. И точно так же она нужна при приеме данных из локальной сети в компьютер. Главное отличие буферной памяти от памяти для временного хранения информации, рассмотренной в предыдущем разделе, состоит в том, что к информационному буферу всегда имеют доступ не одно внешнее устройство, а два (или даже более). Из-за этого иногда существенно усложняется как схема задания адреса микросхемы памяти, так и схема разделения потоков данных (записываемых в память и читаемых из памяти). Рис. 12.11. Двунаправленный информационный буфер Информационные буферы бывают однонаправленными (входными или выходными) и двунаправленными (то есть входными и выходными одновременно - рис. 12.11). Например, буферная память сетевого адаптера двунаправленная, так как она буферирует и информацию, передаваемую в сеть из компьютера, и информацию, принимаемую из сети в компьютер. Двунаправленные буферы всегда сложнее проектировать из-за большего количества потоков данных. Информационные буферы могут обеспечивать периодический обмен между устройствами или непрерывный обмен между ними. Примером буфера с непрерывным режимом обмена может служить контроллер видеомонитора, информация из которого постоянно выдается на видеомонитор, но может изменяться по инициативе компьютера. Информационные буферы с периодическим режимом обмена могут быть организованы по типу FIFO или по типу LIFO. В случае FIFO массив данных читается из памяти одним устройством в том же порядке, в каком он был записан в память другим устройством. Выпускаются даже специальные микросхемы быстродействующей буферной памяти типа FIFO, которые не имеют адресной шины и представляют собой, по сути, многоразрядный сдвиговый регистр. В отличие от обычной микросхемы сдвигового регистра, где читать вдвигаемую информацию можно только тогда, когда она продвинется по всем ячейкам регистра, информацию с выходов буфера FIFO можно начинать читать с выходов сразу же после того, как она начала записываться в его входы. Но мы будем рассматривать здесь только буферы на обычных, традиционных микросхемах памяти, как более универсальные. В случае информационного буфера LIFO массив данных читается из памяти в порядке, противоположном тому, в котором он был записан в память. Такое решение иногда позволяет проще организовать схему перебора адресов памяти. Тем самым, разнообразие информационных буферов огромно. Мы же рассмотрим здесь всего три примера схем буферной памяти. Первая схема - это простейший однонаправленный буфер с периодическим режимом обмена по принципу FIFO (рис. 12.12). Одно устройство записывает информацию в буфер, на другое устройство выдается информация из буфера. Память всегда записывается полностью, по всем адресам, и читается также полностью. Строб записи "–Зап." поступает в режиме записи с частотой, необходимой для записи, строб чтения "–Чт." поступает при чтении с частотой, необходимой для чтения. Шины данных для

...

Читать дальше »

|

|

ОЗУ для временного хранения информации Главное применение микросхем оперативной памяти, непосредственно следующее из ее названия, - это временное хранение цифровой информации, всевозможных массивов кодов, таблиц данных, одиночных чисел и т.д. Цель такого хранения информации состоит в том, чтобы в любой момент иметь возможность быстро ее прочитать для дальнейшей обработки, записи в энергонезависимую память (в ПЗУ, на магнитные носители) или для другого использования. Записанная в оперативную память и непрочитанная затем информация не имеет смысла, так как при выключении питания она безвозвратно пропадет. Другим словами, временное хранение предполагает, что к памяти имеется возможность доступа от какого-то устройства или от какой-то другой части схемы как с операцией записи, так и с операцией чтения (считывания). В зависимости от того, в каком порядке может записываться или читаться информация, существуют две разновидности ОЗУ: ОЗУ с параллельным или произвольным доступом (это наиболее универсальная схема); ОЗУ с последовательным доступом (это более специфическая схема). Параллельный или произвольный доступ наиболее прост и обычно не требует никаких дополнительных элементов, так как именно на этот режим непосредственно рассчитаны микросхемы памяти. В этом режиме можно записывать информацию в любой адрес ОЗУ и читать информацию из любого адреса ОЗУ в произвольном порядке. Однако параллельный доступ требует формирования довольно сложных последовательностей всех входных сигналов памяти. То есть для записи информации необходимо сформировать код адреса записываемой ячейки и только потом подать данные, сопровождаемые управляющими сигналами –CS и –WR (см. рис. 12.2). Точно так же необходимо подавать полный код адреса читаемой ячейки при операции чтения. Этот режим доступа чаще всего применяется в компьютерах и контроллерах, где самыми главными факторами являются универсальность и гибкость использования памяти для самых разных целей. Последовательный доступ к памяти предполагает более простой порядок общения с памятью. В этом случае не надо задавать код адреса записываемой или читаемой ячейки, так как адрес памяти формируется схемой автоматически. Для записи информации надо всего лишь подать код записываемых данных и сопроводить его стробом записи. Для чтения информации надо подать строб чтения и получить читаемые данные. Автоматическое задание адреса при этом осуществляется внутренними счетчиками, меняющими свое состояние по каждому обращению к памяти. Например, десять последовательных циклов записи запишут информацию в десять последовательно расположенных ячеек памяти. Недостаток такого подхода очевиден: мы не имеем возможности записывать или читать ячейки с произвольными адресами в любом порядке. Зато существенно упрощается и ускоряется процедура обмена с памятью (запись и чтение). Мы будем в данном разделе рассматривать именно этот тип памяти, этот тип доступа. Можно выделить три основных типа оперативной памяти с последовательным доступом: память типа "первым вошел - первым вышел" ( FIFO, First In - First Out); память магазинного, стекового типа, работающая по принципу "последним вошел - первым вышел" (LIFO, Last In - First Out). память для хранения массивов данных. Два первых типа памяти подразумевают возможность чередования операций записи и чтения в памяти. При этом память FIFO выдает читаемые данные в том же порядке, в котором они были записаны, а память LIFO - в порядке, обратном тому, в котором они были записаны в память. Память FIFO можно сравнить со сдвиговым регистром, на выходе которого данные появляются в том же порядке, в котором они были в него записаны. А память LIFO обычно сравнивают с магазином для подачи патронов в автомате или пистолете, в котором первым выдается патрон, вставленный в магазин последним. Память с принципом LIFO используется, в частности, в компьютерах ( стек ), где она хранит информацию о параметрах программ и подпрограмм. Для памяти FIFO требуется хранение двух кодов адреса (адрес для записи и адрес для чтения), для памяти LIFO достаточно одного кода адреса. Хранение массивов в памяти предполагает, что сначала в память записывается целиком большой массив данных, а потом этот же массив целиком читается из памяти. Эта память также может быть устроена по двум принципам (FIFO и LIFO). В первом случае (FIFO) записанный массив читается в том же порядке, в котором и был записан, во втором случае (LIFO) - в противоположном порядке (начиная с конца). В обоих этих случаях для общения с памятью требуется хранить только один код адреса памяти. Рассмотрим несколько примеров схем, реализующих перечисленные типы памяти с последовательным доступом. |

|

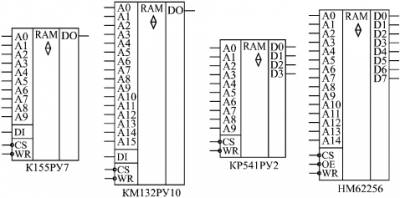

В лекции рассказывается о микросхемах оперативной памяти, алгоритмах их работы, параметрах, типовых схемах включения, а также о способах реализации на их основе некоторых часто встречающихся функций. Содержание ОЗУ для временного хранения информации ОЗУ как информационный буфер Улучшение параметров ОЗУ Основное отличие оперативной памяти (RAM) от постоянной ( ROM ) состоит в возможности оперативного изменения содержимого всех ячеек памяти с помощью дополнительного управляющего сигнала записи WR. Каждая ячейка оперативной (статической) памяти представляет собой, по сути, регистр из триггерных ячеек, в который может быть записана информация и из которого можно информацию читать. Выбор того или иного регистра (той или иной ячейки памяти) производится с помощью кода адреса памяти. Поэтому при выключении питания вся информация из оперативной памяти пропадает (стирается), а при включении питания информация в оперативной памяти может быть произвольной. Отметим, что существует также еще одна разновидность оперативной памяти, так называемая динамическая (в отличие от статической), в которой информация хранится не в регистрах (не в триггерных ячейках), а в виде заряда на конденсаторах. Эта память отличается более низкой стоимостью, меньшим быстродействием и необходимостью регулярной регенерации ("Refresh" - "освежение") информации в ней (так как конденсаторы со временем разряжаются). Область применения динамической памяти гораздо уже, чем статической, в основном она используется в качестве системной оперативной памяти компьютеров, где соображения стоимости выходят на первый план. Поэтому здесь мы о ней говорить не будем, хотя многие особенности использования статической памяти относятся и к динамической памяти. Во всех рассмотренных в предыдущем разделе схемах постоянная память в принципе может быть заменена оперативной, только карту прошивки в данном случае придется записывать в память каждый раз заново после включения питания. Аналогично, многое из сказанного в данном разделе про оперативную память справедливо и для постоянной памяти, но только информацию в постоянной памяти менять невозможно. Однако существуют также и специфические области применения оперативной памяти, которым и будет уделено здесь особое внимание. Рис. 12.1. Примеры микросхем статических ОЗУ Как уже отмечалось, оперативная память бывает двух основных видов: с раздельными шинами входных и выходных данных (в основном это одноразрядная память) и с двунаправленной (совмещенной) шиной входных и выходных данных (многоразрядная память). Некоторые простейшие примеры микросхем памяти обоих этих видов приведены на рис. 12.1. Выходы данных микросхем памяти имеют тип ОК (довольно редко) или 3С. Управляющие сигналы - это сигнал выбора микросхемы CS (иногда их несколько), сигнал записи WR (обычно отрицательный) и иногда сигнал разрешения выхода OE. Микросхема оперативной памяти К155РУ7 (аналог - F9342APC) имеет организацию 1Кх1 и раздельные входной и выходной сигналы данных. Выход микросхемы - типа 3С. Управление работой микросхемы производится двумя управляющими сигналами CS и WR. Режимы работы микросхемы приведены в табл. 12.1. Таблица 12.1. Режимы работы оперативной памяти К155РУ7 Входы и выходы Режим работы -CS -WR A0 A9 DI DO 1 Х Х Х 3С Хранение 0 0 Адрес 0 3С Запись 0

|

|

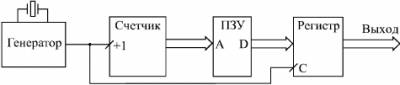

Микропрограммные автоматы представляют собой следующий шаг по пути усложнения интеллекта цифровых схем. На основе микропрограммных автоматов можно строить устройства, которые работают по довольно сложным алгоритмам, выполняют различные функции, определяемые входными сигналами, выдают сложные последовательности выходных сигналов. При этом алгоритм работы микропрограммного автомата может быть легко изменен заменой прошивки ПЗУ. В отличие от рассматривавшихся ранее устройств на "жесткой" логике, принцип работы которых однозначно определяется используемыми элементами и способом их соединения, микропрограммные автоматы с помощью одной и той же схемы могут выполнять самые разные функции. То есть они гораздо более гибкие, чем схемы на "жесткой" логике. К тому же проектировать микропрограммные автоматы с точки зрения схемотехники довольно просто. Недостатком любого микропрограммного автомата по сравнению со схемами на "жесткой" логике является меньшее предельное быстродействие и необходимость составления карты прошивки ПЗУ с микропрограммами, часто довольно сложными. Наиболее распространенная структура микропрограммного автомата (рис. 11.15) включает в себя всего лишь три элемента: ПЗУ, регистр, срабатывающий по фронту, и тактовый генератор. Рис. 11.15. Структура микропрограммного автомата ПЗУ имеет (L+M) адресных разрядов и N разрядов данных. Регистр применяется с количеством разрядов (N + L). Разряды данных ПЗУ записываются в регистр по положительному фронту тактового сигнала с генератора. Часть этих разрядов (М) используется для образования адреса ПЗУ, другая часть (N-M) служит для формирования выходных сигналов. Входные сигналы (L) поступают на входы регистра и используются совместно с частью выходных разрядов ПЗУ для получения адреса ПЗУ. Схема работает следующим образом. В каждом такте ПЗУ выдает код данных, тем самым определяя не только состояние выходных сигналов схемы, но и адрес ПЗУ, который установится в следующем такте (после следующего положительного фронта тактового сигнала). На этот следующий адрес влияют также и входные сигналы. То есть в отличие от формирователя последовательности сигналов, рассмотренного в предыдущем разделе, в данном случае адреса могут перебираться не только последовательно (с помощью счетчика), но и в произвольном порядке, который определяется прошивкой ПЗУ, называемой микропрограммой. Условием правильной работы схемы будет следующее. За один период тактового сигнала должны успеть сработать регистр и ПЗУ. Иначе говоря, сумма задержки регистра и задержки выборки адреса ПЗУ не должна превышать периода тактового сигнала. Отметим также, что входные сигналы микропрограммного автомата нельзя подавать непосредственно на адресные входы ПЗУ (без регистра), так как их асинхронное (по отношению к тактовому сигналу) изменение может вызвать переходный процесс на выходах данных ПЗУ именно в тот момент, когда выходные сигналы ПЗУ записываются в регистр. В результате в регистр может записаться неверная информация, что нарушит работу всей схемы. Регистр же синхронизирует изменения входных сигналов с тактовым сигналом, в результате чего все разряды кода адреса ПЗУ меняется одновременно — по положительному фронту тактового сигнала. Регистр должен обязательно срабатывать по фронту, использование регистра-защелки не допускается, так как он может вызвать лавинообразный переходный процесс. Возможности такой простой схемы оказываются очень большими. Например, микропрограммный автомат может выдавать последовательности выходных сигналов в ответ на определенное изменение входных сигналов. Он может также временно остановить выдачу выходных сигналов до прихода входных сигналов. Он может анализировать длительность входного сигнала и в зависимости от нее выдавать те или иные выходные сигналы. Он может также и многое другое. Сформулируем несколько элементарных функций, из которых могут складываться алгоритмы работы микропрограммного автомата (рис. 11.16): Рис. 11.16. Элементарные функции микропрограммного автомата: последовательный перебор (а), циклическое повторение (б) и остановка (в) Последовательный перебор адресов ПЗУ (например, для выдачи последовательности выходных сигналов). Периодическое повторение последовательности адресов ПЗУ (например, для повторения последователь

...

Читать дальше »

|

|

ПЗУ в генераторах импульсных последовательностей Следующее важнейшее применение ПЗУ — это построение генераторов сложных последовательностей цифровых импульсов. Такие генераторы широко используются в самых разных измерительных системах, в устройствах автоматики, в телевизионных системах, в схемах управления линейными или матричными индикаторами и т.д. Задача в данном случае ставится следующим образом. Необходимо сформировать последовательность из нескольких сигналов различной длительности, сдвинутых относительно друг друга на различные временные интервалы. Причем последовательность эта может быть как разовой (однократно начинающейся по внешнему сигналу), так и периодической, непрерывно повторяющейся. Наиболее распространенная структура генератора последовательностей выходных сигналов на ПЗУ включает в себя тактовый генератор нужной частоты, счетчик с требуемым числом разрядов, ПЗУ и выходной регистр (рис. 11.11). Счетчик перебирает адреса ПЗУ, ПЗУ последовательно выдает на выходы данных все записанные в него коды. Выходной регистр, тактируемый тем же тактовым сигналом, что и счетчик, служит для предотвращения появления в выходных сигналах паразитных импульсов и для обеспечения одновременного переключения всех выходных сигналов (что особенно важно в случае, когда используются несколько параллельно включенных микросхем ПЗУ для увеличения разрядности шины данных). Рис. 11.11. Пример структуры генератора последовательностей сигналов на ПЗУ Рис. 11.12. Временная диаграмма формируемых выходных сигналов Рассмотрим пример. Пусть необходимо непрерывно формировать периодическую последовательность из шести выходных сигналов в соответствии с временной диаграммой рис. 11.12. Получить такую последовательность можно, конечно, с помощью комбинационных схем, включенных на выходе счетчика, или с помощью множества одновибраторов, запускающих друг друга, но и то, и другое решение чересчур громоздко и сложно как в проектировании, так и в настройке. Применение же ПЗУ значительно упрощает задачу. Достаточно провести несложные расчеты и составить карту прошивки ПЗУ. Расчеты сводятся к следующему. Прежде всего определяем минимально возможную тактовую частоту (с целью минимизации требуемого объема ПЗУ ). Для этого надо выделить максимальный временной интервал (дискрет времени), который укладывается целое число раз во все временные сдвиги, задержки, длительности требуемой диаграммы. В нашем случае этот дискрет равен одному делению по оси времени. Например, если длительность этого деления равна 250 нс, то и период тактового сигнала надо выбирать 250 нс, то есть тактовая частота будет равна 4 МГц. Можно, конечно, выбрать ее и кратной 4 МГц, например, 8 МГц, 12 МГц, но тогда потребуется вдвое или втрое больший объем ПЗУ. Если бы нам надо было формировать только три верхних сигнала (Выход 0, Выход 1, Выход 2), то период тактовой частоты можно было бы брать вдвое больше (в нашем примере — 500 нс), так как для этих сигналов все длительности кратны двум делениям. Второй расчет сводится к определению количества ячеек и разрядности ПЗУ. Шесть выходных сигналов схемы требуют шести разрядов данных ПЗУ. Длительность последовательности равна 20 тактам (или 14 в 16-ричном коде), то есть не равна 2n, поэтому счетчик придется сбрасывать в нуль через каждые 20 тактов, для чего потребуется еще один разряд данных ПЗУ. Итого потребуется 7 разрядов. А для перебора 20 тактов последовательности потребуется 5-разрядный счетчик, так как 24 = 16 (недостаточно), а 25 = 32 (достаточно). Значит, разрядность шины адреса ПЗУ также должна быть не менее пяти, то есть минимальные требования к организации ПЗУ — это 32х8, значит, подойдет микросхема ПЗУ типа РЕ3. Наконец, третий расчет касается условий правильной работы схемы. Генератор последовательности будет работать правильно, если за период тактового сигнала успеют сработать счетчик и ПЗУ. То есть сумма задержки полного переключения счетчика и задержки выборки адреса ПЗУ не должна превышать периода тактового сигнала. |

|

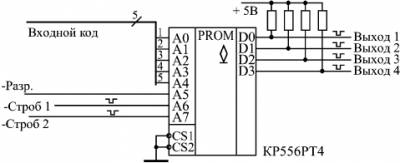

ПЗУ как универсальная комбинационная микросхема Одно из самых распространенных применений микросхем ПЗУ — замена ими сложных комбинационных схем. Такое решение позволяет существенно упростить проектируемое устройство и снизить количество используемых комбинационных микросхем, а иногда даже уменьшить потребляемый ток и увеличить быстродействие схемы. Суть предлагаемого подхода сводится к следующему. Если рассматривать адресные входы микросхемы ПЗУ как входы комбинационной схемы, а разряды данных — как выходы этой комбинационной схемы, то можно сформировать любую требуемую таблицу истинности данной комбинационной схемы. Для этого всего лишь надо составить таблицу прошивки ПЗУ, соответствующую нужной таблице истинности. В этом случае не надо ни подбирать логические элементы, ни оптимизировать их соединения, ни думать о том, можно ли вообще построить заданную комбинационную схему из стандартных микросхем. Важно только, чтобы количество требуемых входов не превышало количества адресных разрядов ПЗУ, а количество требуемых выходов не превышало разрядности шины данных ПЗУ. В качестве примера рассмотрим довольно сложную комбинационную схему (рис. 11.5), имеющую восемь входов и четыре выхода. Функция схемы сводится к следующему. Прежде всего она распознает два различных 5-разрядных входных кода (11001 и 10011) в случае, когда на входе разрешения "–Разр." присутствует нулевой сигнал, а при приходе сигналов "–Строб 1" и "Строб 2" схема выдает на выход отрицательные импульсы. Причем первый выходной сигнал вырабатывается в случае, когда входной код равен 11001 и пришел сигнал "–Строб 1", второй выходной сигнал — при том же коде, но по входному сигналу "–Строб 2". Третий и четвертый выходной сигналы вырабатываются при входном коде 10011 и при приходе соответственно управляющих сигналов "–Строб 1" и "–Строб 2". То есть логика работы довольно сложная и разнообразных логических элементов требуется немало. Рис. 11.5. Пример комбинационной схемы, заменяемой ПЗУ Рис. 11.6. Включение ПЗУ для замены комбинационной схемы, показанной на рис. 11.5 Но всю эту схему можно заменить всего лишь одной микросхемой ПЗУ, например, типа РТ4, имеющей 8 адресных входов и 4 выхода данных (рис. 11.6). При этом пять разрядов входного кода подаются на младшие разряды адреса ПЗУ (А0...А4), входной сигнал "Разр." — на адресный вход А5, сигнал "–Строб 1" — на вход А6, сигнал "–Строб 2" — на вход А7. Младший разряд данных памяти D0 используется для первого выходного сигнала, D1 — для второго выходного сигнала, D2 — для третьего выходного сигнала, D3 — для четвертого выходного сигнала. Микросхема ПЗУ всегда выбрана (управляющие сигналы –CS1 и –CS2 — нулевые). На выходах данных памяти включены резисторы, так как тип выходов микросхемы РТ4 — ОК. Составим карту прошивки ПЗУ. Активные выходные сигналы — нулевые, а пассивные — единичные. Значит, в большинстве ячеек ПЗУ будут записаны коды F (все выходные сигналы пассивны). Активному (нулевому) первому выходному сигналу при пассивных остальных будет соответствовать двоичный код данных 1110 (16-ричный код — Е), активному второму выходному сигналу будет соответствовать двоичный код 1101 (16-ричный — D), активному третьему выходному сигналу — двоичный код 1011 (или В), активному четвертому выходному сигналу — двоичный код 0111 (или 7). То есть только содержимое четырех ячеек памяти будет отличаться от F. Например, код Е будет записан в ячейку с таким адресом, пять младших разрядов которого (A0...А4) равны селектируемому входному коду 11001, разряд А5 равен нулю (сигнал "Разр." активен), разряд А6 равен нулю (сигнал "Строб 1" активен), а разряд А7 равен единице (сигнал "Строб 2" пассивен). Таким образом, получаем двоичный код адреса 10011001 (или в 16-ричном коде 99). Точно так же код D будет записан в ячейку с адресом 01011001 (то есть 16-ричное 59), код В — в ячейку с адресом 10010011 (то есть 93), а код 7 — в ячейку с адресом 01010011 (то есть 53). Получившаяся карта прошивки ПЗУ приведена в табл. 11.2. Она полностью совпадает с таблицей истинности заменяемой комбинационной схемы. Таблица 11.2. Карта прошивки ПЗУ для замены комбинационной схемы Адрес 0

...

Читать дальше »

|

|

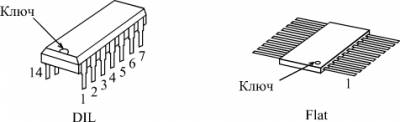

Микросхемы памяти (или просто память, или запоминающие устройства — ЗУ, английское "Memory") представляют собой следующий шаг на пути усложнения цифровых микросхем по сравнению с микросхемами, рассмотренными ранее. Память — это всегда очень сложная структура, включающая в себя множество элементов. Правда, внутренняя структура памяти — регулярная, большинство элементов одинаковые, связи между элементами сравнительно простые, поэтому функции, выполняемые микросхемами памяти, не слишком сложные. Память, как и следует из ее названия, предназначена для запоминания, хранения каких-то массивов информации, проще говоря, наборов, таблиц, групп цифровых кодов. Каждый код хранится в отдельном элементе памяти, называемом ячейкой памяти. Основная функция любой памяти как раз и состоит в выдаче этих кодов на выходы микросхемы по внешнему запросу. А основной параметр памяти — это ее объем, то есть количество кодов, которые могут в ней храниться, и разрядность этих кодов. Для обозначения количества ячеек памяти используются следующие специальные единицы измерения: 1К — это 1024, то есть 210 (читается "кило-"" или "ка-"), примерно равно одной тысяче; 1М — это 1048576, то есть 220 (читается "мега-"), примерно равно одному миллиону; 1Г — это 1073741824, то есть 230 (читается "гига-"), примерно равно одному миллиарду. Принцип организации памяти записывается следующим образом: сначала пишется количество ячеек, а затем через знак умножения (косой крест) — разрядность кода, хранящегося в одной ячейке. Например, организация памяти 64Кх8 означает, что память имеет 64К (то есть 65536) ячеек и каждая ячейка — восьмиразрядная. А организация памяти 4М х 1 означает, что память имеет 4М (то есть 4194304) ячеек, причем каждая ячейка имеет всего один разряд. Общий объем памяти измеряется в байтах (килобайтах — Кбайт, мегабайтах — Мбайт, гигабайтах — Гбайт) или в битах (килобитах — Кбит, мегабитах — Мбит, гигабитах — Гбит). В зависимости от способа занесения (записи) информации и от способа ее хранения, микросхемы памяти разделяются на следующие основные типы: Постоянная память ( ПЗУ — постоянное запоминающее устройство, ROM — Read Only Memory — память только для чтения), в которую информация заносится один раз на этапе изготовления микросхемы. Такая память называется еще масочным ПЗУ. Информация в памяти не пропадает при выключении ее питания, поэтому ее еще называют энергонезависимой памятью. Программируемая постоянная память (ППЗУ — программируемое ПЗУ, PROM — Programmable ROM), в которую информация может заноситься пользователем с помощью специальных методов (ограниченное число раз). Информация в ППЗУ тоже не пропадает при выключении ее питания, то есть она также энергонезависимая. Оперативная память (ОЗУ — оперативное запоминающее устройство, RAM — Random Access Memory — память с произвольным доступом), запись информации в которую наиболее проста и может производиться пользователем сколько угодно раз на протяжении всего срока службы микросхемы. Информация в памяти пропадает при выключении ее питания. Существует множество промежуточных типов памяти, а также множество подтипов, но указанные — самые главные, принципиально отличающиеся друг от друга. Хотя, разница между ПЗУ и ППЗУ с точки зрения разработчика цифровых устройств, как правило, не так уж велика. Только в отдельных случаях, например, при использовании так называемой флэш-памяти (flash-memory), представляющей собой ППЗУ с многократным электрическим стиранием и перезаписью информации, эта разница действительно чрезвычайно важна. Можно считать, что флэш-память занимает промежуточное положение между ОЗУ и ПЗУ. В общем случае любая микросхема памяти имеет следующие информационные выводы (рис. 11.1): Рис. 11.1. Микросхемы памяти: ПЗУ (а), ОЗУ с двунаправленной шиной данных (б), ОЗУ с раздельными шинами входных и выходных данных (в) Адресные выводы (входные), образующие шину адреса памяти. Код на адресных линиях представляет собой двоичный номер ячейки памяти, к которой происходит обращение в данный момент. Количество адресных разрядов определяет количество ячеек памяти: при количестве адресных разрядов n количество ячеек памяти равно 2n. Выводы данных (выходные), образующие шину данных памяти. Код на линиях данных представляет собой содержимое той ячейки памяти, к которой производится обращение в данный момент. Количество разрядов данных определяет количество разрядов всех ячеек памяти (обычно оно бывает равным 1, 4, 8, 16). Как правило, выходы данных имеют тип выходного каскада

...

Читать дальше »

|

|

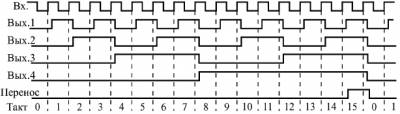

Синхронные (или параллельные) счетчики представляют собой наиболее быстродействующую разновидность счетчиков. Наращивание их разрядности при соблюдении определенных условий не приводит к увеличению полной задержки срабатывания. То есть можно считать, что именно синхронные счетчики работают как идеальные счетчики, все разряды которых срабатывают одновременно, параллельно. Задержка срабатывания счетчика в этом случае примерно равна задержке срабатывания одного триггера. Достигается такое быстродействие существенным усложнением внутренней структуры микросхемы. Вместе с тем недостатком синхронных счетчиков является более сложное управление их работой по сравнению с асинхронными счетчиками и с синхронными счетчиками с асинхронным переносом. Поэтому синхронные счетчики целесообразно применять только в тех случаях, когда действительно требуется очень высокое быстродействие, очень высокая скорость переключения разрядов. Иначе усложнение схемы управления может быть не оправдано. Рис. 10.1. Временная диаграмма работы синхронных двоичных счетчиков Временная диаграмма работы синхронного счетчика (рис. 10.1) отличается от временной диаграммы синхронного счетчика с асинхронным переносом способом формирования сигнала переноса, используемого при каскадировании счетчиков для увеличения разрядности. Сигнал переноса CR (от английского "Carry") вырабатывается в данном случае тогда, когда все выходы счетчика устанавливаются в единицу (при прямом счете) или в нуль (при обратном, инверсном счете). Входной тактовый сигнал в образовании сигнала переноса при этом не участвует. При каскадировании (совместном включении для увеличения разрядности), например, двух счетчиков тактовые входы С обоих счетчиков объединяются, а сигнал переноса первого счетчика подается на вход разрешения счета (ECT) второго счетчика. В результате второй счетчик будет считать каждый шестнадцатый входной тактовый импульс (так как он будет срабатывать только при переносе от первого счетчика). Выходные сигналы второго счетчика будут переключаться по фронту общего тактового сигнала одновременно с выходными сигналами первого счетчика. Условием правильной работы будет в данном случае следующее: за период тактового сигнала должен успеть выработаться сигнал переноса первого счетчика. Рис. 10.2. Синхронные счетчики стандартных серий В стандартные серии микросхем входят несколько разновидностей синхронных (параллельных) счетчиков (рис. 10.2). Различаются они способом счета (двоичные или двоично-десятичные, реверсивные или не реверсивные) и управляющими сигналами (наличием или отсутствием сигнала сброса). Все счетчики считают по положительному фронту тактового сигнала, все имеют выход переноса CR и входы расширения для каскадирования. Все счетчики имеют возможность параллельной записи информации. Таблица 10.1. Режимы работы счетчиков ИЕ9 и ИЕ10 Входы Режим -R -EWR ECR ECT C 0 Х Х Х Х Сброс 1 0 Х Х 0 1 Параллельная запись 1 1 0 Х Х Хранение 1 1

...

Читать дальше »

|

|

Синхронные счетчики с асинхронным переносом Синхронные (или параллельные) счетчики характеризуются тем, что все их разряды в пределах одной микросхемы переключаются одновременно, параллельно. Это достигается существенным усложнением внутренней структуры микросхемы по сравнению с простыми асинхронными счетчиками. В результате полная задержка переключения синхронного счетчика примерно равна задержке одного триггера, то есть синхронные счетчики гораздо быстрее асинхронных, причем их быстродействие не падает с ростом количества разрядов выходного кода (конечно, до определенных пределов). Управление работой синхронного счетчика гораздо сложнее, чем в случае асинхронного счетчика, а количество разрядов синхронных счетчиков обычно не превышает четырех. Поэтому синхронные счетчики не всегда могут успешно конкурировать с асинхронными, особенно при невысоких требованиях к быстродействию. Зато и возможностей у синхронных счетчиков, как правило, гораздо больше, чем у асинхронных, например, они обеспечивают параллельную запись информации в счетчик и инверсный режим счета. Для объединения нескольких синхронных счетчиков с целью увеличения числа их разрядов (для каскадирования) используется специальный выходной сигнал переноса. В зависимости от принципов формирования этого сигнала и от принципов его использования синхронные (параллельные) счетчики делятся на счетчики с асинхронным (последовательным) переноом и счетчики с синхронным (параллельным) переносом (или полностью синхронные счетчики). Синхронные счетчики с асинхронным переносом занимают промежуточное положение по быстродействию между асинхронными счетчиками и полностью синхронными счетчиками. Управление их работой проще, чем у синхронных счетчиков, но сложнее, чем у асинхронных. Работают данные счетчики по положительному фронту входного сигнала (или, что то же самое, по заднему фронту отрицательного сигнала). Основная суть их работы сводится к следующему: все разряды одного счетчика переключаются одновременно, но при каскадировании каждый следующий счетчик (дающий более старшие разряды) переключается с задержкой относительно предыдущего счетчика (дающего более младшие разряды). То есть задержка переключения многоразрядного счетчика увеличивается в данном случае не с каждым новым разрядом (как у асинхронных счетчиков), а с каждой новой микросхемой (например, 4-разрядной). Сигнал переноса у этих счетчиков при прямом счете вырабатывается тогда, когда все разряды равны единице (достигнут максимальный код) и когда приходит входной сигнал. Поэтому сигнал переноса, повторяющий входной сигнал, будет задержан относительно входного сигнала. И именно этот сигнал переноса используется в качестве входного для следующего счетчика при каскадировании. То есть входной сигнал второго счетчика задержан относительно входного сигнала первого счетчика, входной сигнал третьего счетчика задержан относительно входного сигнала второго счетчика и т.д. Временная диаграмма 4-разрядного синхронного счетчика с асинхронным переносом показана на рис. 9.10. Из рисунка видно, что разряды переключаются одновременно по положительному фронту входного сигнала (с некоторой задержкой), а отрицательный сигнал переноса также задержан относительно входного отрицательного импульса. Понятно, что переключение разрядов счетчика, работающего с этим сигналом переноса в качестве входного, будет происходить с дополнительной задержкой относительно переключения разрядов данного счетчика. Рис. 9.10. Временная диаграмма работы синхронного счетчика с асинхронным переносом Примерами синхронных счетчиков с асинхронным переносом могут служить двоично-десятичный счетчик ИЕ6 и двоичный счетчик ИЕ7 (рис. 9.11). Они полностью идентичны по своим возможностям и назначениям входов и выходов, но только ИЕ6 считает от 0 до 9, а ИЕ7 - от 0 до 15. Оба счетчика реверсивные, обеспечивают как прямой счет (по положительному фронту на входе +1), так и обратный счет (по положительному фронту на входе –1). При прямом счете отрицательный сигнал переноса вырабатывается на выходе >15 (у ИЕ7) или >9 (у ИЕ6). При обратном (инверсном) счете отрицательный сигнал переноса вырабатывается на выходе < 0 после достижения выходным кодом значения 0000. Имеется возможность сброса счетчика в нуль положительным сигналом на входе R, а также возможность параллельной записи в счетчик кода со входов D1, D2, D4, D8 по отрицательному сигналу на входе –WR. При параллельной записи информации счетчики ведут себя как регистры-защелки, то есть выходной код счетчика повторяет входной код, пока на входе –WR присутствует сигна

...

Читать дальше »

Категория:

9. Лекция: Асинхронные и синхронно-асинхронные счетчики

|

Просмотров:

2693

|

|

Дата:

11.03.2012

|

|

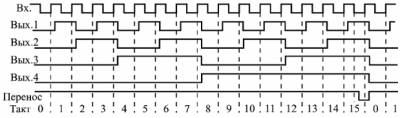

Асинхронные счетчики строятся из простой цепочки JK-триггеров, каждый из которых работает в счетном режиме. Выходной сигнал каждого триггера служит входным сигналом для следующего триггера. Поэтому все разряды (выходы) асинхронного счетчика переключаются последовательно (отсюда название - последовательные счетчики), один за другим, начиная с младшего и кончая старшим. Каждый следующий разряд переключается с задержкой относительно предыдущего (рис. 9.2), то есть, вообще говоря, асинхронно, не одновременно с входным сигналом и с другими разрядами. Чем больше разрядов имеет счетчик, тем большее время ему требуется на полное переключение всех разрядов. Задержка переключения каждого разряда примерно равна задержке триггера, а полная задержка установления кода на выходе счетчика равна задержке одного разряда, умноженной на число разрядов счетчика. Легко заметить, что при периоде входного сигнала, меньшем полной задержки установления кода счетчика, правильный код на выходе счетчика просто не успеет установиться, поэтому такая ситуация не имеет смысла. Это накладывает жесткие ограничения на период (частоту) входного сигнала, причем увеличение, к примеру, вдвое количества разрядов счетчика автоматически уменьшает вдвое предельно допустимую частоту входного сигнала. Рис. 9.2. Временная диаграмма работы 4-разрядного асинхронного счетчика Таким образом, если нам нужен выходной код асинхронного счетчика, то есть все его выходные сигналы (разряды) одновременно, то должно выполняться следующее неравенство: T> Ntз, где T - период входного сигнала, N - число разрядов счетчика, tз - время задержки одного разряда. Надо еще учесть, что за период входного сигнала должно успеть сработать устройство (узел), на которое поступает выходной код счетчика, иначе счетчик просто не нужен; поэтому ограничение на частоту входного сигнала обычно бывает еще жестче. В составе стандартных серий цифровых микросхем асинхронных счетчиков немного. Для примера на рис. 9.3 приведены три из них: 4-х разрядный двоично-десятичный счетчик ИЕ2, 4-х разрядный двоичный счетчик ИЕ5 и 8-и разрядный двоичный счетчик ИЕ19 (он же сдвоенный четырехразрядный счетчик). Рис. 9.3. Асинхронные счетчики стандартных серий У всех этих счетчиков управление работой очень простое, есть всего лишь входы сброса в нуль или входы установки в 9 (только у ИЕ2). Все асинхронные счетчики работают по отрицательному фронту входного сигнала С (или, что то же самое, по заднему фронту положительного входного сигнала). У всех трех счетчиков выделены две независимые части, что увеличивает возможности их применения. При объединении этих двух частей получается счетчик максимальной разрядности. Выходы счетчиков обозначают на схемах 0, 1, 2, 3, ... (как номера разрядов выходного двоичного кода) или 1, 2, 4, 8, ... (как веса каждого разряда двоичного кода). Счетчик ИЕ2 имеет две части: один триггер (вход С1, выход 1) и три триггера (вход С2 и выходы 2, 4, 8). Таким образом, он состоит из одноразрядного счетчика и трехразрядного счетчика. Одиночный триггер работает в обычном счетном режиме, изменяя свое состояние по каждому отрицательному фронту сигнала С1, то есть делит частоту входного сигнала на 2. Три оставшихся триггера включены таким образом, чтобы считать до 5, то есть делить входную частоту сигнала С2 на 9. После достижения кода 4 (то есть 100) на выходах 2, 4 и 8 этот трехразрядный счетчик по следующему отрицательному фронту сигнала С2 сбрасывается в нуль. В результате при объединении выхода 1 микросхемы со входом С2 мы получаем 4-разрядный двоично-десятичный счетчик, делящий частоту входного сигнала С1 на 10 и сбрасывающийся в нуль после достижения на выходах 1, 2, 4, 8 кода 9 (то есть 1001) по отрицательному фронту сигнала С1. Таблица 9.1. Таблица истинности счетчика ИЕ2 Входы Выходы

Категория:

9. Лекция: Асинхронные и синхронно-асинхронные счетчики

|

Просмотров:

1369

|

|

Дата:

11.03.2012

|

|

Счетчики представляют собой более высокий, чем регистры, уровень сложности цифровых микросхем, имеющих внутреннюю память. Хотя в основе любого счетчика лежат те же самые триггеры, которые образуют и регистры, но в счетчиках триггеры соединены более сложными связями, в результате чего их функции - сложнее, и на их основе можно строить более сложные устройства, чем на регистрах. Точно так же, как и в случае регистров, внутренняя память счетчиков - оперативная, то есть ее содержимое сохраняется только до тех пор, пока включено питание схемы. С выключением питания память стирается, а при новом включении питания схемы содержимое памяти будет произвольным, случайным, зависящим только от конкретной микросхемы, то есть выходные сигналы счетчиков будут произвольными. Рис. 9.1. Работа 4-разрядного двоичного счетчика Как следует из самого названия, счетчики предназначены для счета входных импульсов. То есть с приходом каждого нового входного импульса двоичный код на выходе счетчика увеличивается (или уменьшается) на единицу (рис. 9.1). Срабатывать счетчик может по отрицательному фронту входного (тактового) сигнала (как на рисунке) или по положительному фронту. Режим счета обеспечивается использованием внутренних триггеров, работающих в счетном режиме. Выходы счетчика представляют собой как раз выходы этих триггеров. Каждый выход счетчика представляет собой разряд двоичного кода, причем разряд, переключающийся чаще других (по каждому входному импульсу), будет младшим, а разряд, переключающийся реже других, - старшим. Счетчик может работать на увеличение выходного кода по каждому входному импульсу; это основной режим, имеющийся во всех счетчиках, он называется режимом прямого счета. Счетчик может также работать на уменьшение выходного кода по каждому входному импульсу; это режим обратного или инверсного счета, предусмотренный в счетчиках, называемых реверсивными. Инверсный счет бывает довольно удобен в схемах, где необходимо отсчитывать заданное количество входных импульсов. Большинство счетчиков работают в обычном двоичном коде, то есть считают от 0 до (2N–1), где N - число разрядов выходного кода счетчика. Например, 4-разрядный счетчик в режиме прямого счета будет считать от 0 (код 0000) до 15 (код 1111), а 8-разрядный - от 0 (код 0000 0000) до 255 (код 1111 1111). После максимального значения кода счетчик по следующему входному импульсу переключается опять в 0, то есть работает по кругу. Если же счет - инверсный, то счетчик считает до нуля, а дальше переходит к максимальному коду 111...1. Имеются также двоично-десятичные счетчики, предельный код на выходе которых не превышает максимального двоично-десятичного числа, возможного при данном количестве разрядов. Например, 4-разрядный двоично-десятичный счетчик в режиме прямого счета будет считать от 0 (код 0000) до 9 (код 1001), а затем снова от 0 до 9. А 8-разрядный двоично-десятичный счетчик будет считать от 0 (код 0000 0000) до 99 (код 1001 1001). При инверсном счете двоично-десятичные счетчики считают до нуля, а со следующим входным импульсом переходят к максимально возможному двоично-десятичному числу (то есть 9 - для 4-разрядного счетчика, 99 - для 8-разрядного счетчика). Двоично-десятичные счетчики удобны, например, при организации десятичной индикации их выходного кода. Применяются они гораздо реже обычных двоичных счетчиков. По быстродействию все счетчики делятся на три большие группы: Асинхронные счетчики (или последовательные). Синхронные счетчики с асинхронным переносом (или параллельные счетчики с последовательным переносом, синхронно-асинхронные счетчики). Синхронные счетчики (или параллельные). Принципиальные различия между этими группами проявляются только на втором уровне представления, на уровне модели с временными задержками. Причем больше всего различия эти проявляются при каскадировании счетчиков. Наибольшим быстродействием обладают синхронные счетчики, наименьшим - асинхронные счетчики, наиболее просто управляемые среди других. Каждая группа счетчиков имеет свои области применения, на которых мы и остановимся.

Категория:

9. Лекция: Асинхронные и синхронно-асинхронные счетчики

|

Просмотров:

634

|

|

Дата:

11.03.2012

|

|

|