Микропрограммные автоматы представляют собой следующий шаг по пути усложнения интеллекта цифровых схем. На основе микропрограммных автоматов можно строить устройства, которые работают по довольно сложным алгоритмам, выполняют различные функции, определяемые входными сигналами, выдают сложные последовательности выходных сигналов. При этом алгоритм работы микропрограммного автомата может быть легко изменен заменой прошивки ПЗУ. В отличие от рассматривавшихся ранее устройств на "жесткой" логике, принцип работы которых однозначно определяется используемыми элементами и способом их соединения, микропрограммные автоматы с помощью одной и той же схемы могут выполнять самые разные функции. То есть они гораздо более гибкие, чем схемы на "жесткой" логике. К тому же проектировать микропрограммные автоматы с точки зрения схемотехники довольно просто. Недостатком любого микропрограммного автомата по сравнению со схемами на "жесткой" логике является меньшее предельное быстродействие и необходимость составления карты прошивки ПЗУ с микропрограммами, часто довольно сложными. Наиболее распространенная структура микропрограммного автомата (рис. 11.15) включает в себя всего лишь три элемента: ПЗУ, регистр, срабатывающий по фронту, и тактовый генератор. Рис. 11.15. Структура микропрограммного автомата ПЗУ имеет (L+M) адресных разрядов и N разрядов данных. Регистр применяется с количеством разрядов (N + L). Разряды данных ПЗУ записываются в регистр по положительному фронту тактового сигнала с генератора. Часть этих разрядов (М) используется для образования адреса ПЗУ, другая часть (N-M) служит для формирования выходных сигналов. Входные сигналы (L) поступают на входы регистра и используются совместно с частью выходных разрядов ПЗУ для получения адреса ПЗУ. Схема работает следующим образом. В каждом такте ПЗУ выдает код данных, тем самым определяя не только состояние выходных сигналов схемы, но и адрес ПЗУ, который установится в следующем такте (после следующего положительного фронта тактового сигнала). На этот следующий адрес влияют также и входные сигналы. То есть в отличие от формирователя последовательности сигналов, рассмотренного в предыдущем разделе, в данном случае адреса могут перебираться не только последовательно (с помощью счетчика), но и в произвольном порядке, который определяется прошивкой ПЗУ, называемой микропрограммой. Условием правильной работы схемы будет следующее. За один период тактового сигнала должны успеть сработать регистр и ПЗУ. Иначе говоря, сумма задержки регистра и задержки выборки адреса ПЗУ не должна превышать периода тактового сигнала. Отметим также, что входные сигналы микропрограммного автомата нельзя подавать непосредственно на адресные входы ПЗУ (без регистра), так как их асинхронное (по отношению к тактовому сигналу) изменение может вызвать переходный процесс на выходах данных ПЗУ именно в тот момент, когда выходные сигналы ПЗУ записываются в регистр. В результате в регистр может записаться неверная информация, что нарушит работу всей схемы. Регистр же синхронизирует изменения входных сигналов с тактовым сигналом, в результате чего все разряды кода адреса ПЗУ меняется одновременно — по положительному фронту тактового сигнала. Регистр должен обязательно срабатывать по фронту, использование регистра-защелки не допускается, так как он может вызвать лавинообразный переходный процесс. Возможности такой простой схемы оказываются очень большими. Например, микропрограммный автомат может выдавать последовательности выходных сигналов в ответ на определенное изменение входных сигналов. Он может также временно остановить выдачу выходных сигналов до прихода входных сигналов. Он может анализировать длительность входного сигнала и в зависимости от нее выдавать те или иные выходные сигналы. Он может также и многое другое. Сформулируем несколько элементарных функций, из которых могут складываться алгоритмы работы микропрограммного автомата (рис. 11.16): Рис. 11.16. Элементарные функции микропрограммного автомата: последовательный перебор (а), циклическое повторение (б) и остановка (в) Последовательный перебор адресов ПЗУ (например, для выдачи последовательности выходных сигналов). Периодическое повторение последовательности адресов ПЗУ (например, для повторения последователь

...

Читать дальше »

|

ПЗУ в генераторах импульсных последовательностей

Следующее важнейшее применение ПЗУ — это построение генераторов сложных последовательностей цифровых импульсов. Такие генераторы широко используются в самых разных измерительных системах, в устройствах автоматики, в телевизионных системах, в схемах управления линейными или матричными индикаторами и т.д.

Задача в данном случае ставится следующим образом. Необходимо сформировать последовательность из нескольких сигналов различной длительности, сдвинутых относительно друг друга на различные временные интервалы. Причем последовательность эта может быть как разовой (однократно начинающейся по внешнему сигналу), так и периодической, непрерывно повторяющейся.

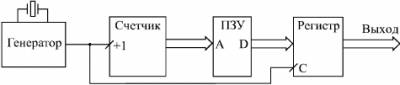

Наиболее распространенная структура генератора последовательностей выходных сигналов на ПЗУ включает в себя тактовый генератор нужной частоты, счетчик с требуемым числом разрядов, ПЗУ и выходной регистр (рис. 11.11). Счетчик перебирает адреса ПЗУ, ПЗУ последовательно выдает на выходы данных все записанные в него коды. Выходной регистр, тактируемый тем же тактовым сигналом, что и счетчик, служит для предотвращения появления в выходных сигналах паразитных импульсов и для обеспечения одновременного переключения всех выходных сигналов (что особенно важно в случае, когда используются несколько параллельно включенных микросхем ПЗУ для увеличения разрядности шины данных).

Рис. 11.11. Пример структуры генератора последовательностей сигналов на ПЗУ

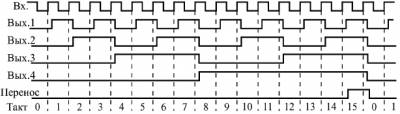

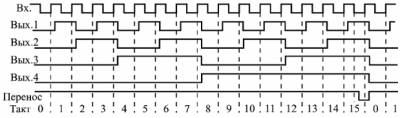

Рис. 11.12. Временная диаграмма формируемых выходных сигналов Рассмотрим пример. Пусть необходимо непрерывно формировать периодическую последовательность из шести выходных сигналов в соответствии с временной диаграммой рис. 11.12. Получить такую последовательность можно, конечно, с помощью комбинационных схем, включенных на выходе счетчика, или с помощью множества одновибраторов, запускающих друг друга, но и то, и другое решение чересчур громоздко и сложно как в проектировании, так и в настройке. Применение же ПЗУ значительно упрощает задачу. Достаточно провести несложные расчеты и составить карту прошивки ПЗУ.

Расчеты сводятся к следующему.

Прежде всего определяем минимально возможную тактовую частоту (с целью минимизации требуемого объема ПЗУ ). Для этого надо выделить максимальный временной интервал (дискрет времени), который укладывается целое число раз во все временные сдвиги, задержки, длительности требуемой диаграммы. В нашем случае этот дискрет равен одному делению по оси времени. Например, если длительность этого деления равна 250 нс, то и период тактового сигнала надо выбирать 250 нс, то есть тактовая частота будет равна 4 МГц. Можно, конечно, выбрать ее и кратной 4 МГц, например, 8 МГц, 12 МГц, но тогда потребуется вдвое или втрое больший объем ПЗУ. Если бы нам надо было формировать только три верхних сигнала (Выход 0, Выход 1, Выход 2), то период тактовой частоты можно было бы брать вдвое больше (в нашем примере — 500 нс), так как для этих сигналов все длительности кратны двум делениям.

Второй расчет сводится к определению количества ячеек и разрядности ПЗУ. Шесть выходных сигналов схемы требуют шести разрядов данных ПЗУ. Длительность последовательности равна 20 тактам (или 14 в 16-ричном коде), то есть не равна 2n, поэтому счетчик придется сбрасывать в нуль через каждые 20 тактов, для чего потребуется еще один разряд данных ПЗУ. Итого потребуется 7 разрядов. А для перебора 20 тактов последовательности потребуется 5-разрядный счетчик, так как 24 = 16 (недостаточно), а 25 = 32 (достаточно). Значит, разрядность шины адреса ПЗУ также должна быть не менее пяти, то есть минимальные требования к организации ПЗУ — это 32х8, значит, подойдет микросхема ПЗУ типа РЕ3.

Наконец, третий расчет касается условий правильной работы схемы. Генератор последовательности будет работать правильно, если за период тактового сигнала успеют сработать счетчик и ПЗУ. То есть сумма задержки полного переключения счетчика и задержки выборки адреса ПЗУ не должна превышать периода тактового сигнала.

|

ПЗУ как универсальная комбинационная микросхема

Одно из самых распространенных применений микросхем ПЗУ — замена ими сложных комбинационных схем. Такое решение позволяет существенно упростить проектируемое устройство и снизить количество используемых комбинационных микросхем, а иногда даже уменьшить потребляемый ток и увеличить быстродействие схемы.

Суть предлагаемого подхода сводится к следующему. Если рассматривать адресные входы микросхемы ПЗУ как входы комбинационной схемы, а разряды данных — как выходы этой комбинационной схемы, то можно сформировать любую требуемую таблицу истинности данной комбинационной схемы. Для этого всего лишь надо составить таблицу прошивки ПЗУ, соответствующую нужной таблице истинности. В этом случае не надо ни подбирать логические элементы, ни оптимизировать их соединения, ни думать о том, можно ли вообще построить заданную комбинационную схему из стандартных микросхем. Важно только, чтобы количество требуемых входов не превышало количества адресных разрядов ПЗУ, а количество требуемых выходов не превышало разрядности шины данных ПЗУ.

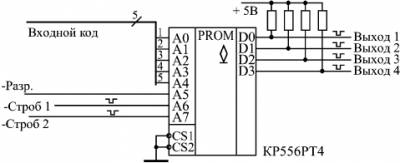

В качестве примера рассмотрим довольно сложную комбинационную схему (рис. 11.5), имеющую восемь входов и четыре выхода. Функция схемы сводится к следующему. Прежде всего она распознает два различных 5-разрядных входных кода (11001 и 10011) в случае, когда на входе разрешения "–Разр." присутствует нулевой сигнал, а при приходе сигналов "–Строб 1" и "Строб 2" схема выдает на выход отрицательные импульсы. Причем первый выходной сигнал вырабатывается в случае, когда входной код равен 11001 и пришел сигнал "–Строб 1", второй выходной сигнал — при том же коде, но по входному сигналу "–Строб 2". Третий и четвертый выходной сигналы вырабатываются при входном коде 10011 и при приходе соответственно управляющих сигналов "–Строб 1" и "–Строб 2". То есть логика работы довольно сложная и разнообразных логических элементов требуется немало.

Рис. 11.5. Пример комбинационной схемы, заменяемой ПЗУ

Рис. 11.6. Включение ПЗУ для замены комбинационной схемы, показанной на рис. 11.5 Но всю эту схему можно заменить всего лишь одной микросхемой ПЗУ, например, типа РТ4, имеющей 8 адресных входов и 4 выхода данных (рис. 11.6). При этом пять разрядов входного кода подаются на младшие разряды адреса ПЗУ (А0...А4), входной сигнал "Разр." — на адресный вход А5, сигнал "–Строб 1" — на вход А6, сигнал "–Строб 2" — на вход А7. Младший разряд данных памяти D0 используется для первого выходного сигнала, D1 — для второго выходного сигнала, D2 — для третьего выходного сигнала, D3 — для четвертого выходного сигнала. Микросхема ПЗУ всегда выбрана (управляющие сигналы –CS1 и –CS2 — нулевые). На выходах данных памяти включены резисторы, так как тип выходов микросхемы РТ4 — ОК.

Составим карту прошивки ПЗУ. Активные выходные сигналы — нулевые, а пассивные — единичные. Значит, в большинстве ячеек ПЗУ будут записаны коды F (все выходные сигналы пассивны). Активному (нулевому) первому выходному сигналу при пассивных остальных будет соответствовать двоичный код данных 1110 (16-ричный код — Е), активному второму выходному сигналу будет соответствовать двоичный код 1101 (16-ричный — D), активному третьему выходному сигналу — двоичный код 1011 (или В), активному четвертому выходному сигналу — двоичный код 0111 (или 7). То есть только содержимое четырех ячеек памяти будет отличаться от F.

Например, код Е будет записан в ячейку с таким адресом, пять младших разрядов которого (A0...А4) равны селектируемому входному коду 11001, разряд А5 равен нулю (сигнал "Разр." активен), разряд А6 равен нулю (сигнал "Строб 1" активен), а разряд А7 равен единице (сигнал "Строб 2" пассивен). Таким образом, получаем двоичный код адреса 10011001 (или в 16-ричном коде 99). Точно так же код D будет записан в ячейку с адресом 01011001 (то есть 16-ричное 59), код В — в ячейку с адресом 10010011 (то есть 93), а код 7 — в ячейку с адресом 01010011 (то есть 53). Получившаяся карта прошивки ПЗУ приведена в табл. 11.2. Она полностью совпадает с таблицей истинности заменяемой комбинационной схемы.

Таблица 11.2. Карта прошивки ПЗУ для замены комбинационной схемы

|

Микросхемы памяти (или просто память, или запоминающие устройства — ЗУ, английское "Memory") представляют собой следующий шаг на пути усложнения цифровых микросхем по сравнению с микросхемами, рассмотренными ранее. Память — это всегда очень сложная структура, включающая в себя множество элементов. Правда, внутренняя структура памяти — регулярная, большинство элементов одинаковые, связи между элементами сравнительно простые, поэтому функции, выполняемые микросхемами памяти, не слишком сложные.

Память, как и следует из ее названия, предназначена для запоминания, хранения каких-то массивов информации, проще говоря, наборов, таблиц, групп цифровых кодов. Каждый код хранится в отдельном элементе памяти, называемом ячейкой памяти. Основная функция любой памяти как раз и состоит в выдаче этих кодов на выходы микросхемы по внешнему запросу. А основной параметр памяти — это ее объем, то есть количество кодов, которые могут в ней храниться, и разрядность этих кодов.

Для обозначения количества ячеек памяти используются следующие специальные единицы измерения:

1К — это 1024, то есть 210 (читается "кило-"" или "ка-"), примерно равно одной тысяче; 1М — это 1048576, то есть 220 (читается "мега-"), примерно равно одному миллиону; 1Г — это 1073741824, то есть 230 (читается "гига-"), примерно равно одному миллиарду. Принцип организации памяти записывается следующим образом: сначала пишется количество ячеек, а затем через знак умножения (косой крест) — разрядность кода, хранящегося в одной ячейке. Например, организация памяти 64Кх8 означает, что память имеет 64К (то есть 65536) ячеек и каждая ячейка — восьмиразрядная. А организация памяти 4М х 1 означает, что память имеет 4М (то есть 4194304) ячеек, причем каждая ячейка имеет всего один разряд. Общий объем памяти измеряется в байтах (килобайтах — Кбайт, мегабайтах — Мбайт, гигабайтах — Гбайт) или в битах (килобитах — Кбит, мегабитах — Мбит, гигабитах — Гбит).

В зависимости от способа занесения (записи) информации и от способа ее хранения, микросхемы памяти разделяются на следующие основные типы:

Постоянная память ( ПЗУ — постоянное запоминающее устройство, ROM — Read Only Memory — память только для чтения), в которую информация заносится один раз на этапе изготовления микросхемы. Такая память называется еще масочным ПЗУ. Информация в памяти не пропадает при выключении ее питания, поэтому ее еще называют энергонезависимой памятью. Программируемая постоянная память (ППЗУ — программируемое ПЗУ, PROM — Programmable ROM), в которую информация может заноситься пользователем с помощью специальных методов (ограниченное число раз). Информация в ППЗУ тоже не пропадает при выключении ее питания, то есть она также энергонезависимая. Оперативная память (ОЗУ — оперативное запоминающее устройство, RAM — Random Access Memory — память с произвольным доступом), запись информации в которую наиболее проста и может производиться пользователем сколько угодно раз на протяжении всего срока службы микросхемы. Информация в памяти пропадает при выключении ее питания. Существует множество промежуточных типов памяти, а также множество подтипов, но указанные — самые главные, принципиально отличающиеся друг от друга. Хотя, разница между ПЗУ и ППЗУ с точки зрения разработчика цифровых устройств, как правило, не так уж велика. Только в отдельных случаях, например, при использовании так называемой флэш-памяти (flash-memory), представляющей собой ППЗУ с многократным электрическим стиранием и перезаписью информации, эта разница действительно чрезвычайно важна. Можно считать, что флэш-память занимает промежуточное положение между ОЗУ и ПЗУ.

В общем случае любая микросхема памяти имеет следующие информационные выводы (рис. 11.1): Рис. 11.1. Микросхемы памяти: ПЗУ (а), ОЗУ с двунаправленной шиной данных (б), ОЗУ с раздельными шинами входных и выходных данных (в) Адресные выводы (входные), образующие шину адреса памяти. Код на адресных линиях представляет собой двоичный номер ячейки памяти, к которой происходит обращение в данный момент. Количество адресных разрядов определяет количество ячеек памяти: при количестве адресных разрядов n количество ячеек памяти равно 2n. Выводы данных (выходные), образующие шину данных памяти. Код на линиях данных представляет собой содержимое той ячейки памяти, к которой производится обращение в данный момент. Количество разрядов данных определяет количество разрядов всех ячеек памяти (обычно оно бывает равным 1, 4, 8, 16). Как правило, выходы данных имеют тип выходного каскада

...

Читать дальше »

|

Синхронные (или параллельные) счетчики представляют собой наиболее быстродействующую разновидность счетчиков. Наращивание их разрядности при соблюдении определенных условий не приводит к увеличению полной задержки срабатывания. То есть можно считать, что именно синхронные счетчики работают как идеальные счетчики, все разряды которых срабатывают одновременно, параллельно. Задержка срабатывания счетчика в этом случае примерно равна задержке срабатывания одного триггера. Достигается такое быстродействие существенным усложнением внутренней структуры микросхемы.

Вместе с тем недостатком синхронных счетчиков является более сложное управление их работой по сравнению с асинхронными счетчиками и с синхронными счетчиками с асинхронным переносом. Поэтому синхронные счетчики целесообразно применять только в тех случаях, когда действительно требуется очень высокое быстродействие, очень высокая скорость переключения разрядов. Иначе усложнение схемы управления может быть не оправдано.

Рис. 10.1. Временная диаграмма работы синхронных двоичных счетчиков Временная диаграмма работы синхронного счетчика (рис. 10.1) отличается от временной диаграммы синхронного счетчика с асинхронным переносом способом формирования сигнала переноса, используемого при каскадировании счетчиков для увеличения разрядности. Сигнал переноса CR (от английского "Carry") вырабатывается в данном случае тогда, когда все выходы счетчика устанавливаются в единицу (при прямом счете) или в нуль (при обратном, инверсном счете). Входной тактовый сигнал в образовании сигнала переноса при этом не участвует.

При каскадировании (совместном включении для увеличения разрядности), например, двух счетчиков тактовые входы С обоих счетчиков объединяются, а сигнал переноса первого счетчика подается на вход разрешения счета (ECT) второго счетчика. В результате второй счетчик будет считать каждый шестнадцатый входной тактовый импульс (так как он будет срабатывать только при переносе от первого счетчика). Выходные сигналы второго счетчика будут переключаться по фронту общего тактового сигнала одновременно с выходными сигналами первого счетчика. Условием правильной работы будет в данном случае следующее: за период тактового сигнала должен успеть выработаться сигнал переноса первого счетчика. Рис. 10.2. Синхронные счетчики стандартных серий В стандартные серии микросхем входят несколько разновидностей синхронных (параллельных) счетчиков (рис. 10.2). Различаются они способом счета (двоичные или двоично-десятичные, реверсивные или не реверсивные) и управляющими сигналами (наличием или отсутствием сигнала сброса). Все счетчики считают по положительному фронту тактового сигнала, все имеют выход переноса CR и входы расширения для каскадирования. Все счетчики имеют возможность параллельной записи информации.

Таблица 10.1. Режимы работы счетчиков ИЕ9 и ИЕ10 Входы Режим -R -EWR ECR ECT C 0 Х Х Х Х Сброс 1 0 Х Х 0 1 Параллельная запись 1 1 0 Х Х Хранение

|

Синхронные счетчики с асинхронным переносом

Синхронные (или параллельные) счетчики характеризуются тем, что все их разряды в пределах одной микросхемы переключаются одновременно, параллельно. Это достигается существенным усложнением внутренней структуры микросхемы по сравнению с простыми асинхронными счетчиками. В результате полная задержка переключения синхронного счетчика примерно равна задержке одного триггера, то есть синхронные счетчики гораздо быстрее асинхронных, причем их быстродействие не падает с ростом количества разрядов выходного кода (конечно, до определенных пределов).

Управление работой синхронного счетчика гораздо сложнее, чем в случае асинхронного счетчика, а количество разрядов синхронных счетчиков обычно не превышает четырех. Поэтому синхронные счетчики не всегда могут успешно конкурировать с асинхронными, особенно при невысоких требованиях к быстродействию. Зато и возможностей у синхронных счетчиков, как правило, гораздо больше, чем у асинхронных, например, они обеспечивают параллельную запись информации в счетчик и инверсный режим счета.

Для объединения нескольких синхронных счетчиков с целью увеличения числа их разрядов (для каскадирования) используется специальный выходной сигнал переноса. В зависимости от принципов формирования этого сигнала и от принципов его использования синхронные (параллельные) счетчики делятся на счетчики с асинхронным (последовательным) переноом и счетчики с синхронным (параллельным) переносом (или полностью синхронные счетчики).

Синхронные счетчики с асинхронным переносом занимают промежуточное положение по быстродействию между асинхронными счетчиками и полностью синхронными счетчиками. Управление их работой проще, чем у синхронных счетчиков, но сложнее, чем у асинхронных. Работают данные счетчики по положительному фронту входного сигнала (или, что то же самое, по заднему фронту отрицательного сигнала). Основная суть их работы сводится к следующему: все разряды одного счетчика переключаются одновременно, но при каскадировании каждый следующий счетчик (дающий более старшие разряды) переключается с задержкой относительно предыдущего счетчика (дающего более младшие разряды). То есть задержка переключения многоразрядного счетчика увеличивается в данном случае не с каждым новым разрядом (как у асинхронных счетчиков), а с каждой новой микросхемой (например, 4-разрядной).

Сигнал переноса у этих счетчиков при прямом счете вырабатывается тогда, когда все разряды равны единице (достигнут максимальный код) и когда приходит входной сигнал. Поэтому сигнал переноса, повторяющий входной сигнал, будет задержан относительно входного сигнала. И именно этот сигнал переноса используется в качестве входного для следующего счетчика при каскадировании. То есть входной сигнал второго счетчика задержан относительно входного сигнала первого счетчика, входной сигнал третьего счетчика задержан относительно входного сигнала второго счетчика и т.д.

Временная диаграмма 4-разрядного синхронного счетчика с асинхронным переносом показана на рис. 9.10. Из рисунка видно, что разряды переключаются одновременно по положительному фронту входного сигнала (с некоторой задержкой), а отрицательный сигнал переноса также задержан относительно входного отрицательного импульса. Понятно, что переключение разрядов счетчика, работающего с этим сигналом переноса в качестве входного, будет происходить с дополнительной задержкой относительно переключения разрядов данного счетчика. Рис. 9.10. Временная диаграмма работы синхронного счетчика с асинхронным переносом Примерами синхронных счетчиков с асинхронным переносом могут служить двоично-десятичный счетчик ИЕ6 и двоичный счетчик ИЕ7 (рис. 9.11). Они полностью идентичны по своим возможностям и назначениям входов и выходов, но только ИЕ6 считает от 0 до 9, а ИЕ7 - от 0 до 15. Оба счетчика реверсивные, обеспечивают как прямой счет (по положительному фронту на входе +1), так и обратный счет (по положительному фронту на входе –1). При прямом счете отрицательный сигнал переноса вырабатывается на выходе >15 (у ИЕ7) или >9 (у ИЕ6). При обратном (инверсном) счете отрицательный сигнал переноса вырабатывается на выходе < 0 после достижения выходным кодом значения 0000. Имеется возможность сброса счетчика в нуль положительным сигналом на входе R, а также возможность параллельной записи в счетчик кода со входов D1, D2, D4, D8 по отрицательному сигналу на входе –WR. При параллельной записи информации счетчики ведут себя как регистры-защелки, то есть выходной код счетчика повторяет входной код, пока на входе –WR присутствует сигна

...

Читать дальше »

|

Асинхронные счетчики строятся из простой цепочки JK-триггеров, каждый из которых работает в счетном режиме. Выходной сигнал каждого триггера служит входным сигналом для следующего триггера. Поэтому все разряды (выходы) асинхронного счетчика переключаются последовательно (отсюда название - последовательные счетчики), один за другим, начиная с младшего и кончая старшим. Каждый следующий разряд переключается с задержкой относительно предыдущего (рис. 9.2), то есть, вообще говоря, асинхронно, не одновременно с входным сигналом и с другими разрядами.

Чем больше разрядов имеет счетчик, тем большее время ему требуется на полное переключение всех разрядов. Задержка переключения каждого разряда примерно равна задержке триггера, а полная задержка установления кода на выходе счетчика равна задержке одного разряда, умноженной на число разрядов счетчика. Легко заметить, что при периоде входного сигнала, меньшем полной задержки установления кода счетчика, правильный код на выходе счетчика просто не успеет установиться, поэтому такая ситуация не имеет смысла. Это накладывает жесткие ограничения на период (частоту) входного сигнала, причем увеличение, к примеру, вдвое количества разрядов счетчика автоматически уменьшает вдвое предельно допустимую частоту входного сигнала. Рис. 9.2. Временная диаграмма работы 4-разрядного асинхронного счетчика Таким образом, если нам нужен выходной код асинхронного счетчика, то есть все его выходные сигналы (разряды) одновременно, то должно выполняться следующее неравенство: T> Ntз, где T - период входного сигнала, N - число разрядов счетчика, tз - время задержки одного разряда.

Надо еще учесть, что за период входного сигнала должно успеть сработать устройство (узел), на которое поступает выходной код счетчика, иначе счетчик просто не нужен; поэтому ограничение на частоту входного сигнала обычно бывает еще жестче.

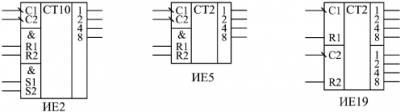

В составе стандартных серий цифровых микросхем асинхронных счетчиков немного. Для примера на рис. 9.3 приведены три из них: 4-х разрядный двоично-десятичный счетчик ИЕ2, 4-х разрядный двоичный счетчик ИЕ5 и 8-и разрядный двоичный счетчик ИЕ19 (он же сдвоенный четырехразрядный счетчик). Рис. 9.3. Асинхронные счетчики стандартных серий У всех этих счетчиков управление работой очень простое, есть всего лишь входы сброса в нуль или входы установки в 9 (только у ИЕ2). Все асинхронные счетчики работают по отрицательному фронту входного сигнала С (или, что то же самое, по заднему фронту положительного входного сигнала). У всех трех счетчиков выделены две независимые части, что увеличивает возможности их применения. При объединении этих двух частей получается счетчик максимальной разрядности. Выходы счетчиков обозначают на схемах 0, 1, 2, 3, ... (как номера разрядов выходного двоичного кода) или 1, 2, 4, 8, ... (как веса каждого разряда двоичного кода).

Счетчик ИЕ2 имеет две части: один триггер (вход С1, выход 1) и три триггера (вход С2 и выходы 2, 4, 8). Таким образом, он состоит из одноразрядного счетчика и трехразрядного счетчика. Одиночный триггер работает в обычном счетном режиме, изменяя свое состояние по каждому отрицательному фронту сигнала С1, то есть делит частоту входного сигнала на 2. Три оставшихся триггера включены таким образом, чтобы считать до 5, то есть делить входную частоту сигнала С2 на 9. После достижения кода 4 (то есть 100) на выходах 2, 4 и 8 этот трехразрядный счетчик по следующему отрицательному фронту сигнала С2 сбрасывается в нуль. В результате при объединении выхода 1 микросхемы со входом С2 мы получаем 4-разрядный двоично-десятичный счетчик, делящий частоту входного сигнала С1 на 10 и сбрасывающийся в нуль после достижения на выходах 1, 2, 4, 8 кода 9 (то есть 1001) по отрицательному фронту сигнала С1.

Таблица 9.1. Таблица истинности счетчика ИЕ2 Входы Выходы

|

Счетчики представляют собой более высокий, чем регистры, уровень сложности цифровых микросхем, имеющих внутреннюю память. Хотя в основе любого счетчика лежат те же самые триггеры, которые образуют и регистры, но в счетчиках триггеры соединены более сложными связями, в результате чего их функции - сложнее, и на их основе можно строить более сложные устройства, чем на регистрах. Точно так же, как и в случае регистров, внутренняя память счетчиков - оперативная, то есть ее содержимое сохраняется только до тех пор, пока включено питание схемы. С выключением питания память стирается, а при новом включении питания схемы содержимое памяти будет произвольным, случайным, зависящим только от конкретной микросхемы, то есть выходные сигналы счетчиков будут произвольными.

Рис. 9.1. Работа 4-разрядного двоичного счетчика Как следует из самого названия, счетчики предназначены для счета входных импульсов. То есть с приходом каждого нового входного импульса двоичный код на выходе счетчика увеличивается (или уменьшается) на единицу (рис. 9.1). Срабатывать счетчик может по отрицательному фронту входного (тактового) сигнала (как на рисунке) или по положительному фронту. Режим счета обеспечивается использованием внутренних триггеров, работающих в счетном режиме. Выходы счетчика представляют собой как раз выходы этих триггеров. Каждый выход счетчика представляет собой разряд двоичного кода, причем разряд, переключающийся чаще других (по каждому входному импульсу), будет младшим, а разряд, переключающийся реже других, - старшим.

Счетчик может работать на увеличение выходного кода по каждому входному импульсу; это основной режим, имеющийся во всех счетчиках, он называется режимом прямого счета. Счетчик может также работать на уменьшение выходного кода по каждому входному импульсу; это режим обратного или инверсного счета, предусмотренный в счетчиках, называемых реверсивными. Инверсный счет бывает довольно удобен в схемах, где необходимо отсчитывать заданное количество входных импульсов.

Большинство счетчиков работают в обычном двоичном коде, то есть считают от 0 до (2N–1), где N - число разрядов выходного кода счетчика. Например, 4-разрядный счетчик в режиме прямого счета будет считать от 0 (код 0000) до 15 (код 1111), а 8-разрядный - от 0 (код 0000 0000) до 255 (код 1111 1111). После максимального значения кода счетчик по следующему входному импульсу переключается опять в 0, то есть работает по кругу. Если же счет - инверсный, то счетчик считает до нуля, а дальше переходит к максимальному коду 111...1.

Имеются также двоично-десятичные счетчики, предельный код на выходе которых не превышает максимального двоично-десятичного числа, возможного при данном количестве разрядов. Например, 4-разрядный двоично-десятичный счетчик в режиме прямого счета будет считать от 0 (код 0000) до 9 (код 1001), а затем снова от 0 до 9. А 8-разрядный двоично-десятичный счетчик будет считать от 0 (код 0000 0000) до 99 (код 1001 1001). При инверсном счете двоично-десятичные счетчики считают до нуля, а со следующим входным импульсом переходят к максимально возможному двоично-десятичному числу (то есть 9 - для 4-разрядного счетчика, 99 - для 8-разрядного счетчика). Двоично-десятичные счетчики удобны, например, при организации десятичной индикации их выходного кода. Применяются они гораздо реже обычных двоичных счетчиков.

По быстродействию все счетчики делятся на три большие группы:

Асинхронные счетчики (или последовательные). Синхронные счетчики с асинхронным переносом (или параллельные счетчики с последовательным переносом, синхронно-асинхронные счетчики). Синхронные счетчики (или параллельные). Принципиальные различия между этими группами проявляются только на втором уровне представления, на уровне модели с временными задержками. Причем больше всего различия эти проявляются при каскадировании счетчиков. Наибольшим быстродействием обладают синхронные счетчики, наименьшим - асинхронные счетчики, наиболее просто управляемые среди других. Каждая группа счетчиков имеет свои области применения, на которых мы и остановимся.

|

Сдвиговые регистры

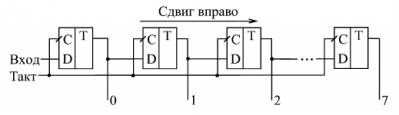

Регистры сдвига или сдвиговые регистры (англ. shift register) представляют собой, как уже отмечалось, последовательно соединенную цепочку триггеров. Основной режим их работы - это сдвиг разрядов кода, записанного в эти триггеры, То есть по тактовому сигналу содержимое каждого предыдущего триггера переписывается в следующий по порядку в цепочке триггер. Код, хранящийся в регистре, с каждым тактом сдвигается на один разряд в сторону старших разрядов или в сторону младших разрядов, что и дало название регистрам данного типа.

В связи с названием направления сдвига в сдвиговых регистрах часто возникает путаница. Сдвиг бывает двух видов: вправо (основной режим, который есть у всех сдвиговых регистров) и влево (этот режим есть только у некоторых, реверсивных сдвиговых регистров). Названия эти отражают внутреннюю структуру регистров сдвига (рис. 8.14) и перезапись сигналов последовательно по цепочке триггеров. При этом триггеры, вполне естественно, нумеруются слева направо, например, от 0 до 7 (или от 1 до 8) для 8-разрядных регистров. В результате сдвиг информации регистром вправо представляет собой сдвиг в сторону разрядов, имеющих большие номера, а сдвиг информации регистром влево - это сдвиг в сторону разрядов, имеющих меньшие номера.

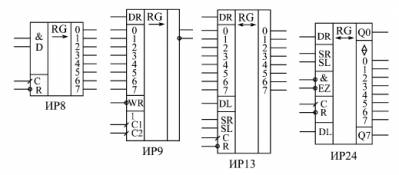

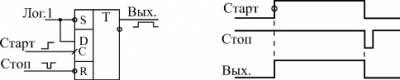

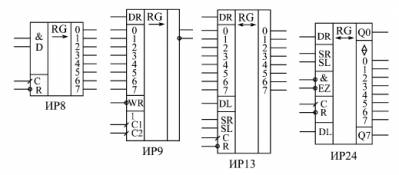

Однако, как известно, в любом двоичном числе слева расположены старшие разряды, а справа - младшие разряды. Поэтому сдвиг двоичного числа вправо будет сдвигом в сторону младших разрядов, а сдвиг влево - сдвигом в сторону старших разрядов. Это противоречие, не чей-то злой умысел, просто так исторически сложилось, и об этом надо помнить разработчику цифровой аппаратуры.Рис. 8.14. Направление сдвига в сдвиговых регистрахВ стандартные серии цифровых микросхем входит несколько типов сдвиговых регистров, отличающихся возможными режимами работы, режимами записи, чтения и сдвига, а также типом выходных каскадов (2С или 3С). Большинство регистров сдвига имеет восемь разрядов. На рис. 8.15 представлены для примера четыре типа микросхем регистров сдвига.

Регистр ИР8 - наиболее простой из регистров сдвига. Он представляет собой 8-разрядную линию задержки, то есть имеет только один информационный вход, на который подается последовательная сдвигаемая информация (точнее, два входа, объединенных по функции 2И), и восемь параллельных выходов. Сдвиг в сторону выходов со старшими номерами осуществляется по переднему фронту тактового сигнала С. Имеется также вход сброса –R, по нулевому сигналу на котором все выходы регистра сбрасываются в нуль. Таблица истинности регистра ИР8 приведена в табл. 8.5.

Рис. 8.15. Сдвиговые регистрыТаблица 8.5. Таблица истинности регистра сдвига ИР8Входы Выходы

|

Регистры, срабатывающие по уровню

Параллельные регистры, срабатывающие по уровню стробирующего сигнала (или, как их еще называют, регистры-защелки, английское "Latch"), можно рассматривать как некий гибрид между буфером и регистром. Когда сигнал на стробирующем входе - единичный, такой регистр пропускает через себя входные информационные сигналы, а когда стробирующий сигнал становится равен нулю, регистр переходит в режим хранения последнего из пропущенных значений входных сигналов.

Применение таких регистров сильно ограничено, хотя иногда они довольно удобны. В некоторых схемах они могут успешно заменять регистры, срабатывающие по фронту, а в других схемах их применение вместо регистров, срабатывающих по фронту, недопустимо.

В стандартных сериях регистры, срабатывающие по уровню, представлены гораздо меньше, чем регистры, срабатывающие по фронту. На рис. 8.10 показаны в качестве примеров две микросхемы 4-разрядного регистра ТМ7 и 8-разрядного регистра ИР22. Стробирующие входы С нередко на схемах обозначают E (от английского "Enable" - "разрешение"), для того чтобы не путать их с тактовыми входами D-триггеров. Рис. 8.10. Регистры, срабатывающие по уровню Микросхему ТМ7 (и близкую к ней ТМ5) часто называют набором триггеров, но ее можно рассматривать и как регистр. Микросхема состоит из четырех триггеров, стробирующие входы которых С соединены попарно, то есть можно говорить о двух двухразрядных регистрах-защелках. Входы С1 и С2 микросхемы управляют каждый двумя разрядами данных. Все триггеры имеют как прямые, так и инверсные выходы, что иногда очень удобно. Таблица истинности микросхемы ТМ7 приведена в табл. 8.3.

При единице на входе С выходные сигналы повторяют входные, то есть регистр работает как обычный буфер с прямыми и инверсными выходами. При нуле на входе С на выходе регистра постоянно хранится та входная информация, которая была в момент прихода отрицательного фронта сигнала С. Однако говорить, что регистр ТМ7 срабатывает по отрицательному фронту сигнала С, неверно, так как информация на выходе меняется не только по этому фронту, но и в момент изменения входных сигналов при С = 1.

Таблица 8.3. Таблица истинности регистра ТМ7 Входы Выходы D C Q -Q 0 1 0 1 1 1 1 0 0 0 Не меняется 1 0 Не меняется Регистр ИР22 отличается от ТМ7 тем, что имеет выходы с тремя состояниями (и соответственно, вход разрешения всех выходов –EZ) и тем, что всеми восемью разрядами управляет один стробирующий сигнал С. Суть работы от этого не изменяется. При единице на входе С регистр работает как буфер-повторитель, а при нуле на входе С - хранит ту информацию, которая была на входе в момент отрицательного фронта сигнала С. Выходы у регистра ИР22 - только прямые. Как и все регистры с тремя состояниями выхода, ИР22 имеет повышенную нагрузочную способность. В табл. 8.4 приведена таблица истинности регистра ИР22.

Таблица 8.4. Таблица истинности регистра ИР22 Входы Выход -EZ C D Q 0 1 1 1 0 1 0 0

|

Принцип действия регистров, срабатывающих по фронту тактового сигнала, ничем не отличается от принципа действия D-триггера. По положительному фронту тактового сигнала С каждый из выходов регистра устанавливается в тот уровень, который был в этот момент на соответствующем данному выходу входе D, и сохраняется таковым до прихода следующего положительного фронта сигнала С. То есть если триггер запоминает один сигнал (один двоичный разряд, один бит), то регистр запоминает сразу несколько (4, 6, 8, 16) сигналов (несколько разрядов, битов). Память регистра сохраняется до момента выключения питания схемы.

Рис. 8.2. Параллельные регистры стандартных серий, срабатывающие по фронту В стандартные серии входит несколько типов параллельных регистров, срабатывающих по фронту (рис. 8.2). Различаются они количеством разрядов, наличием или отсутствием инверсных выходов, наличием или отсутствием входа сброса (–R) или разрешения записи (–WE), а также типом выходных каскадов (2С или 3С) и, соответственно, наличием или отсутствием входа разрешения –EZ. Иногда на схемах тактовый вход С обозначается WR - сигнал записи в регистр.

Большинство регистров имеют восемь разрядов, то есть запоминают один байт информации. Регистр ТМ8 в справочниках обычно называется счетверенным D-триггером (он и в наименовании несет буквы ТМ), хотя он вполне может рассматриваться и как регистр, так как тактовый вход С и вход сброса –R у всех четырех триггеров объединены между собой.

Таблицы истинности регистров очень просты и не отличаются принципиально от таблицы истинности D-триггеров. Отличие от триггеров появляется только в случае наличия у регистра дополнительных управляющих входов разрешения записи –WE и разрешения выхода –EZ. В качестве примеров в табл. 8.1 приведена таблица истинности регистра ИР27, а в табл. 8.2 - регистра ИР37. По переходу тактового сигнала С из 0 в 1 (положительный фронт) оба регистра записывают в себя входную информацию.

Таблица 8.1. Таблица истинности регистра ИР27 Входы Выходы -WE C D Q 0 0 1 0 0 0 0 1 1 1 0 0 X Не меняется 0 1 Х Не меняется 1 Х Х Не меняется Таблица 8.2. Таблица истинности регистра ИР37 Входы Выходы -EZ C D Q 0 0 1 0 0 0 0 1 1 1 0 0 X Не меняется 0 1 Х Не меняется

|

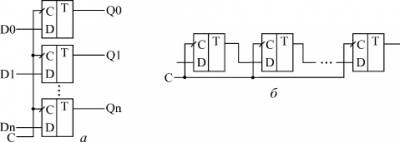

Регистры (англ. register) представляют собой, по сути, несколько D-триггеров (обычно от 4 до 16), соединенных между собой тем или иным способом. Поэтому принципиальной разницы между ними и отдельными D-триггерами не существует. Правда, триггеры, входящие в состав регистров, не имеют такого количества разнообразных управляющих входов, как одиночные триггеры.

На схемах регистры обозначаются буквами RG. В отечественных сериях микросхем регистрам соответствуют буквы ИР. Все регистры делятся на две большие группы (рис. 8.1):

Параллельные регистры; Регистры сдвига (или сдвиговые регистры). Существуют регистры и других типов, но они применяются гораздо реже, чем параллельные и сдвиговые, так как имеют узкоспециальное назначение.

В параллельных регистрах (а) каждый из триггеров имеет свой независимый информационный вход (D) и свой независимый информационный выход. Тактовые входы (С) всех триггеров соединены между собой. В результате параллельный регистр представляет собой многоразрядный, многовходовый триггер.

Рис. 8.1. Структура параллельного регистра (а)и сдвигового регистра (б) В сдвиговых регистрах (б) все триггеры соединены в последовательную цепочку (выход каждого предыдущего триггера соединен со входом D следующего триггера). Тактовые входы всех триггеров (С) объединены между собой. В результате такой триггер может рассматриваться как линия задержки, входной сигнал которой последовательно перезаписывается из триггера в триггер по фронту тактового сигнала С. Информационные входы и выходы триггеров могут быть выведены наружу, а могут и не выводиться - в зависимости от функции, выполняемой регистром.

Параллельные регистры, в свою очередь, делятся на две группы:

Регистры, срабатывающие по фронту управляющего сигнала С (или тактируемые регистры). Регистры, срабатывающие по уровню управляющего сигнала С (или стробируемые регистры). Чаще всего в цифровых схемах используются регистры, управляемые фронтом (то есть тактируемые), однако и стробируемые регистры имеют свой круг задач, в которых их ничто не может заменить.

|

Основные схемы включения триггеров

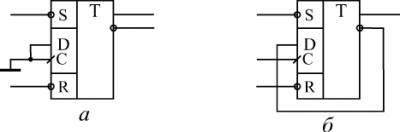

Говоря об областях применения триггеров, мы будем рассматривать исключительно D-триггеры, так как в большинстве случаев RS- и JK-триггеры могут быть заменены D-триггерами без ухудшения каких бы то ни было параметров схемы. Примеры такой замены показаны на рис. 7.5.

RS-триггер получается из D-триггера, если в D-триггере не использовать входы C и D, например, соединить их с общим проводом (а).

Рис. 7.5. Включение D-триггера для замены RS-триггера (а) и JK-триггера в счетном режиме (б) Сложнее обстоит дело с заменой JK-триггера, в котором предусмотрено больше возможностей, чем в D-триггере. Однако обычно два информационных входа JK-триггера не так уж и нужны. А что касается счетного режима, в котором, пожалуй, наиболее часто работают JK-триггеры, то он легко реализуется на D-триггере в результате объединения информационного входа D с инверсным выходом (б). При этом по каждому положительному фронту сигнала С триггер будет менять свое состояние на противоположное: нуль на прямом выходе будет сменяться единицей и наоборот. То есть частота входного сигнала триггера будет меньше частоты входного тактового сигнала С в два раза.

Отметим также, что для реализации счетного режима чаще всего используются не триггеры, а счетчики, которые будут рассмотрены в следующей лекции.

Особенности триггеров обусловливают наиболее широкий диапазон схем их включения для решения самых разных задач.

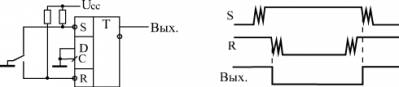

Например, с помощью триггера (любого типа) очень просто и эффективно решается задача устранения влияния дребезга контактов механических переключателей (рис. 7.6). Правда в данном случае необходим тумблер (или кнопка) с тремя выводами, один из которых попеременно подключается к двум другим. При этом первый отрицательный импульс на входе –R перебрасывает триггер в состояние нуля, а первый отрицательный импульс на входе –S — в состояние единицы. Последующие же импульсы на обоих этих входах, вызванные дребезгом контактов, уже никак не влияют на триггер. Нижнее (по рисунку) положение выключателя соответствует нулю на выходе триггера, а верхнее — единице.

Рис. 7.6. Подавление дребезга контактов выключателя с помощью триггера Основное применение триггеры находят в тех случаях, когда надо сформировать сигнал, длительность которого соответствует длительности какой-то выполняемой операции, какого-то продолжительного процесса в схеме. Выходной сигнал триггера при этом может разрешать этот самый процесс, а может информировать остальные узлы устройства о том, что процесс идет (или, как говорят, служить флагом процесса). Например, в схеме на рис. 7.7 в начале процесса (операции) по сигналу "Старт" триггер перебрасывается в единицу, а в конце процесса (операции) по сигналу "Стоп" — обратно в нуль.

Рис. 7.7. Использование триггера в качестве флага процесса Для сигналов "Старт" и "Стоп" можно, конечно, использовать входы триггера -R и -S. Однако более правильным и универсальным решением будет выбор пары входов С и -R или С и -S, что предотвратит неоднозначность поведения триггера при одновременном приходе сигналов "Старт" и "Стоп". Если используются входы С и -R, то на вход D надо подать единицу, а если применяются входы С и -S, то на вход D надо подать нуль. Такое решение удобно еще и тем, что в качестве одного из сигналов "Старт" и "Стоп" может выступать не уровень, а фронт. Именно этот фронт (в нужной полярности) и надо подать в этом случае на тактовый вход триггера С.

Вторая важнейшая область применения триггеров — синхронизация сигналов.

Например, триггер позволяет наиболее просто избавиться от паразитных коротких импульсов на выходах комбинационных схем, возникающих при почти одновременном изменении нескольких входных сигналов (рис. 7.8). Для синхронизации в данном случае необходимо иметь синхросигнал (синхропереход), сопровождающий входные информационные сигналы (входной код) и задержанный относительно момента изменения этих сигналов на время tз

...

Читать дальше »

|

Триггеры

Принцип работы и разновидности триггеров

В основе любого триггера (англ. — "тrigger" или "flip-flop") лежит схема из двух логических элементов, которые охвачены положительными обратными связями (то есть сигналы с выходов подаются на входы). В результате подобного включения схема может находиться в одном из двух устойчивых состояний, причем находиться сколь угодно долго, пока на нее подано напряжение питания.

Рис. 7.1. Схема триггерной ячейки Пример такой схемы (так называемой триггерной ячейки) на двух двухвходовых элементах И-НЕ представлен на рис. 7.1. У схемы есть два инверсных входа: –R — сброс (от английского Reset), и –S — установка (от английского Set), а также два выхода: прямой выход Q и инверсный выход –Q.

Для правильной работы схемы отрицательные импульсы должны поступать на ее входы не одновременно. Приход импульса на вход -R переводит выход -Q в состояние единицы, а так как сигнал -S при этом единичный, выход Q становится нулевым. Этот же сигнал Q поступает по цепи обратной связи на вход нижнего элемента. Поэтому даже после окончания импульса на входе -R состояние схемы не изменяется (на Q остается нуль, на -Q остается единица). Точно так же при приходе импульса на вход -S выход Q в единицу, а выход -Q — в нуль. Оба эти устойчивых состояния триггерной ячейки могут сохраняться сколь угодно долго, пока не придет очередной входной импульс, — иными словами, схема обладает памятью.

Если оба входных импульса придут строго одновременно, то в момент действия этих импульсов на обоих выходах будут единичные сигналы, а после окончания входных импульсов выходы случайным образом попадут в одно из двух устойчивых состояний. Точно так же случайным образом будет выбрано одно из двух устойчивых состояний триггерной ячейки при включении питания. Временная диаграмма работы триггерной ячейки показана на рисунке.

Таблица 7.1. Таблица истинности триггерной ячейки Входы Выходы -R -S Q -Q 0 1 0 1 1 0 1 0 1 1 Без изменения 0 0 Не определено В стандартные серии цифровых микросхем входит несколько типов микросхем триггеров, различающихся методами управления, а также входными и выходными сигналами. На схемах триггеры обозначаются буквой Т. В отечественных сериях микросхем триггеры имеют наименование ТВ, ТМ и ТР в зависимости от типа триггера. Наиболее распространены три типа ( рис. 7.2):

RS-триггер (обозначается ТР) — самый простой триггер, но редко используемый (а). JK-триггер (обозначается ТВ) имеет самое сложное управление, также используется довольно редко (б). D-триггер (обозначается ТМ) — наиболее распространенный тип триггера (в). Примером RS-триггера является микросхема ТР2, в одном корпусе которой находятся четыре RS-триггера. Два триггера имеют по одному входу –R и –S, а два других триггера — по одному входу –R и по два входа –S1 и –S2, объединенных по функции И. Все триггеры имеют только по одному прямому выходу. RS-триггер практически ничем не отличается по своим функциям от триггерной ячейки, рассмотренной ранее (см. рис. 7.1). Отрицательный импульс на входе –R перебрасывает выход в нуль, а отрицательный импульс на входе –S (или на любом из входов –S1 и –S2) перебрасывает выход в единицу. Одновременные сигналы на входах –R и –S переводят выход в единицу, а после окончания импульсов триггер попадает случайным образом в одно из своих устойчивых состояний. Таблица истинности триггера ТР2 с двумя входами установки –S1 и –S2 представлена в табл. 7.2.

$IMAGE $ Рис. 7.2. Триггеры трех основных типов Таблица 7.2. Таблица истинности RS-триггера ТР2

| |